晶振究竟在PCB設計中有個怎么樣的地位,是主角還是配角?通過下面幾方面全面了解晶振在PCB設計中的地位如何?

一、問題描述

某行車記錄儀,測試的時候要加一個外接適配器,在機器上電運行測試時發現超標,具體頻點是84MHZ、144MH、168MHZ,需要分析其輻射超標產生的原因,并給出相應的對策。輻射測試數據如下:

二、輻射源頭分析

該產品只有一塊PCB,其上有一個12MHZ的晶體。其中超標頻點恰好都是12MHZ的倍頻,而分析該機器容易EMI輻射超標的屏和攝像頭,發現LCD-CLK是33MHZ,而攝像頭MCLK是24MHZ;

通過排除發現去掉攝像頭后,超標點依然存在,而通過屏蔽12MZH晶體,超標點有降低,由此判斷144MHZ超標點與晶體有關,PCB布局如下:

三、輻射產生的原理

從PCB布局可以看出,12MHZ的晶體正好布置在了PCB邊緣,當產品放置與輻射發射的測試環境中時,被測產品的高速器件與實驗室中參考接地會形成一定的容性耦合,產生寄生電容,導致出現共模輻射,寄生電容越大,共模輻射越強;

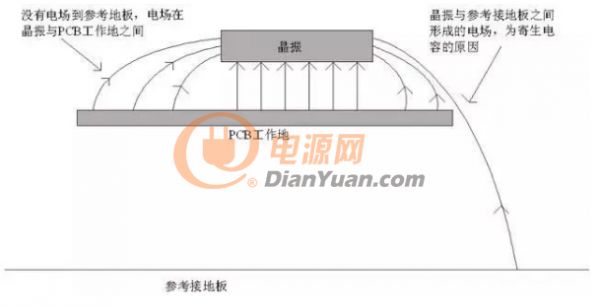

而寄生電容實質就是晶體與參考地之間的電場分布,當兩者之間電壓恒定時,兩者之間電場分布越多,兩者之間電場強度就越大,寄生電容也會越大,晶體在PCB邊緣與在PCB中間時電場分布如下:

PCB邊緣的晶振與參考接地板之間的電場分布示意圖

PCB中間的晶振與參考接地板之間的電場分布示意圖

從圖中可以看出,當晶振布置在PCB中間,或離PCB邊緣較遠時,由于PCB中工作地(GND)平面的存在,使大部分的電場控制在晶振與工作地之間,即在PCB內部,分布到參考接地板去的電場大大減小,導致輻射發射就降低了。

四、處理措施

將晶振內移,使其離PCB邊緣至少1cm以上的距離,并在PCB表層離晶振1cm的范圍內敷銅,同時把表層的銅通過過孔與PCB地平面相連。經過修改后的測試結果頻譜圖如下,從圖可以看出,輻射發射有了明顯改善。

五、思考與啟示

高速的印制線或器件與參考接地板之間的容性耦合,會產生EMI問題,敏感印制線或器件布置在PCB邊緣會產生抗擾度問題。

如果設計中由于其他一些原因一定要布置在PCB邊緣,那么可以在印制線邊上再布一根工作地線,并多增加過孔將此工作地線與工作地平面相連。

聲明:本內容為作者獨立觀點,不代表電源網。本網站原創內容,如需轉載,請注明出處;本網站轉載的內容(文章、圖片、視頻)等資料版權歸原作者所有。如我們采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯系我們,以便迅速采取適當處理措施;歡迎投稿,郵箱∶editor@netbroad.com。

| 優化簡易PCB電路板的大規模測試,提高生產效率 | 24-11-26 15:38 |

|---|---|

| AC-DC控制器PCB布局指南 | 24-07-10 11:12 |

| 瑞薩電子選用Altium作為統一PCB開發工具 并加速合作伙伴和客戶的解決方案設計 | 23-06-27 15:12 |

| 混合信號PCB布局設計的基本準則 | 23-04-14 11:54 |

| Cadence推出Allegro X AI,旨在加速PCB設計流程,可將周轉時間縮短10倍以上 | 23-04-07 10:21 |

| 微信關注 | ||

|

| 技術專題 | 更多>> | |

|

| 技術專題之EMC |

|

| 技術專題之PCB |