?1.DDR

DDR是Double Data Rate的縮寫,即“雙比特翻轉(zhuǎn)”。DDR是一種技術(shù),中國大陸工程師習(xí)慣用DDR稱呼用了DDR技術(shù)的SDRAM,而在中國臺(tái)灣以及歐美,工程師習(xí)慣用DRAM來稱呼。DDR的核心要義是在一個(gè)時(shí)鐘周期內(nèi),上升沿和下降沿都做一次數(shù)據(jù)采樣,這樣400MHz的主頻可以實(shí)現(xiàn)800Mbps的數(shù)據(jù)傳輸速率。我們看下各個(gè)版本的速度對(duì)比

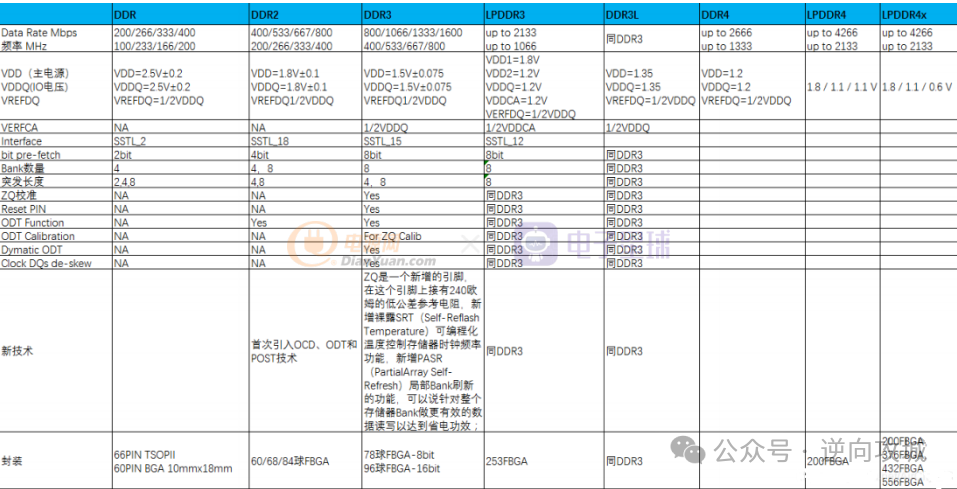

從上可以得知,每個(gè)版本對(duì)應(yīng)的工作頻率有多種,當(dāng)然硬件跟軟件不一樣不必知道這么清楚,只需要知道幾個(gè)常規(guī)頻率就好。

很多知識(shí)點(diǎn)的梳理,大家網(wǎng)上能找到大篇幅的參考,本文就說幾個(gè)常用的和面試中面試官最喜歡問的幾個(gè)點(diǎn)來講。

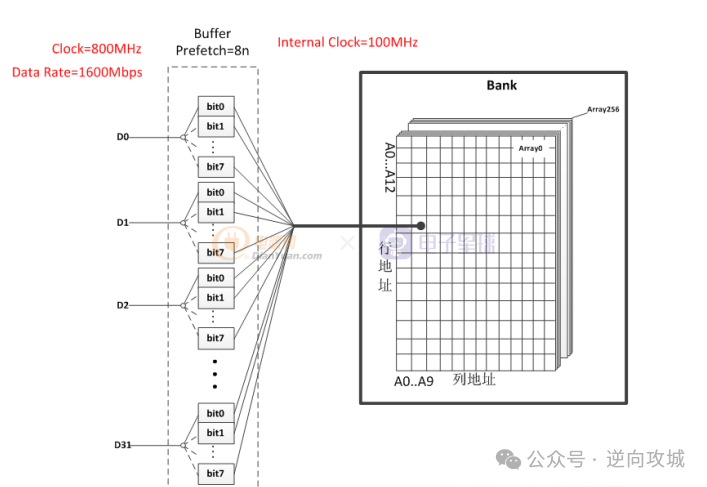

VTT為DDR的地址線,控制線等信號(hào)提供上拉電源,上拉電阻是50Ω左右。VTT=1/2VDDQ,并且VTT要跟隨VDDQ,因此需要專用的電源同時(shí)提供VDDQ和VTT,在Fly-by的拓?fù)渲校?/span>VTT提供電流,增強(qiáng)DDR信號(hào)線的驅(qū)動(dòng)能力。 DDR3的時(shí)鐘是800MHz,Data Rate是1600Mbps,由于這個(gè)Buffer的存在,DDR內(nèi)部的時(shí)鐘只需要200MHz就可以了(注意DDR內(nèi)部不是雙比特翻轉(zhuǎn)采樣)。

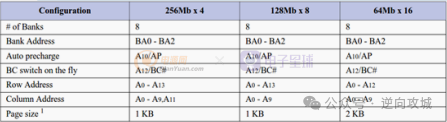

DDR內(nèi)部的最小存儲(chǔ)單元(1bit)是一個(gè)晶體管+一個(gè)電容,電容會(huì)放電,需要不斷的“刷新”(充電)才能保持正常的工作狀態(tài),由于電容充放電需要時(shí)間,DDR內(nèi)部的頻率受限于此,目前技術(shù)一般在100~200MHz。因此需要用Prefetch技術(shù)來提內(nèi)部數(shù)據(jù)高吞吐率(其實(shí)就是串并轉(zhuǎn)換原理)。Prefetch位寬的提高,是DDR2,3,4非常顯著的變化。1.DDR的容量計(jì)算:DDR3 1Gb的尋址配置,以其中128Mbx8為例說明,其中x8表示IO數(shù)據(jù)(DQ)位寬度。

2.ODT

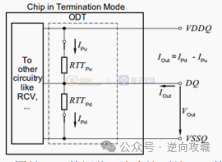

是內(nèi)建核心的終結(jié)電阻,它的功能是讓一些信號(hào)在終結(jié)電阻處消耗完,防止這些信號(hào)在電路上形成反射。換句話說就是在片內(nèi)設(shè)置合適的上下拉電阻,以獲得更好的信號(hào)完整性。被ODT校準(zhǔn)的信號(hào)包括:DQ, DQS, DQS# and DMfor x4 configurationDQ, DQS, DQS#, DM, TDQS and TDQS# for X8 configurationDQU, DQL, DQSU, DQSU#, DQSL, DQSL#, DMUand DML for X16 當(dāng)一個(gè)CPU掛了很多個(gè)DDR芯片的時(shí)候,他們是共用控制線,地址線的,走線肯定要分叉,如果沒有中端匹配電阻,肯定會(huì)產(chǎn)生信號(hào)完整性問題。那么如果只有一個(gè)DDR芯片的時(shí)候,需不需要呢?正常情況下,走線很短,有符合規(guī)則,是不需要的。下圖是DDR中的IO上下拉電阻,RON是DDR的輸出結(jié)構(gòu)的上下拉電阻,RTT是DDR輸入結(jié)構(gòu)的上下拉電阻。這兩個(gè)電阻的阻值都是可調(diào)的

DDR3的PIN定義上有一個(gè)引腳是ODT,如果ODT=0,DRAMTermination State功能關(guān)閉;ODT=1,DRAMTermination State的功能參考寄存器設(shè)置。因?yàn)镈RAM Termination State非常耗電,所以不用的時(shí)候最好不要打開

3.ZQ信號(hào)

在DDR3時(shí)代開始引入,要求在ZQ引腳放置一個(gè)240Ω±1%的高精度電阻到地,注意必須是高精度。而且這個(gè)電阻是必須的,不能省略的。進(jìn)行ODT時(shí),是以這個(gè)引腳上的阻值為參考來進(jìn)行校準(zhǔn)的。校準(zhǔn)需要調(diào)整內(nèi)部電阻,以獲得更好的信號(hào)完整性,但是內(nèi)部電阻隨著溫度會(huì)有些細(xì)微的變化,為了將這個(gè)變化糾正回來,就需要一個(gè)外部的精確電阻作為參考。

4.OCD

是在 DDR-II 開始加入的新功能,而且這個(gè)功能是可選的,有的資料上面又叫離線驅(qū)動(dòng)調(diào)整。OCD的主要作用在于調(diào)整 I/O 接口端的電壓,來補(bǔ)償上拉與下拉電阻值, 從而調(diào)整DQS 與DQ 之間的同步確保信號(hào)的完整與可靠性。 調(diào)校期間,分別測(cè)試 DQS 高電平和 DQ高電平,以及 DQS 低電平和 DQ 高電平的同步情況。

如果不滿足要求,則通過設(shè)定突發(fā)長(zhǎng)度的地址線來傳送上拉 / 下拉電阻等級(jí)(加一檔或減一檔),直到測(cè)試合格才退出 OCD 操作,通過 OCD 操作來減少 DQ 、 DQS的傾斜從而提高信號(hào)的完整性及控制電壓來提高信號(hào)品質(zhì)。由于在一般情況下對(duì)應(yīng)用環(huán)境穩(wěn)定程度要求并不太高,只要存在差分 DQS時(shí)就基本可以保證同步的準(zhǔn)確性, 而且 OCD 的調(diào)整對(duì)其他操作也有一定影響, 因此 OCD 功能在普通臺(tái)式機(jī)上并沒有什么作用,其優(yōu)點(diǎn)主要體現(xiàn)在對(duì)數(shù)據(jù)完整性非常敏感的服務(wù)器等高端產(chǎn)品領(lǐng)域。

5.DDR走線

DDR的信號(hào)線需要分組:-數(shù)據(jù)線一組(DQ,DQS,DQM),誤差控制在20mil以內(nèi);-控制線一組(Address,控制線,時(shí)鐘),以時(shí)鐘為中心,誤差控制在100mil以內(nèi)。

小結(jié):

1.DDR本人目前使用得中覺得三星得確實(shí)穩(wěn)定好用,其他基本都是東芝,海力士等等老外得品牌,國產(chǎn)用的相對(duì)較少。

2.DDR還有一個(gè)致命問題,每一批做出來的板子需要重新適配DDR,否則容易工作不穩(wěn)定,這也是多數(shù)人遇到的問題,目前來說沒啥解決的好方案,面試的老司機(jī)套方案也是套不出來的,這跟PCB的制程,制造工藝有關(guān),暫無好的解決辦法,歡迎大家留言說說有啥辦法解決每一批板子的差異。

3.DDR走線目前常規(guī)的兩種是T型或者菊花鏈的拓步走線方式,這里還是奉勸大家,嚴(yán)格按照廠家推薦走線拓?fù)洌詈媚苤苯訉?duì)抄,這一塊問題比較多,走線麻煩復(fù)雜,重新打板周期也長(zhǎng),成本也不小,不要輕易嘗試,除非你想多麻煩一下軟件兄弟,調(diào)半天都不穩(wěn)定。