在UC3842芯片的應用電路中如果需要進行斜坡補償的,有時可以利用芯片內部震蕩電路產生的三角波來實現,這里分析一下此震蕩電路產生原理及相關參數設計。

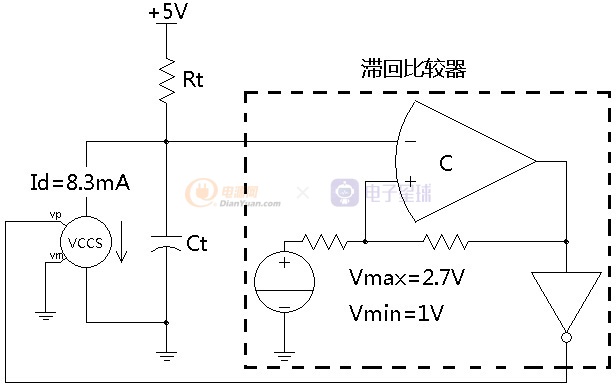

芯片內部震蕩電路等效原理如下:

圖1 UC3842內部震蕩電路

震蕩電路由RC充電、恒流放電及滯回比較器構成。分析結果通過Saber仿真軟件驗證,仿真軟件測得的滯回比較器上限是2.7V下限是1V與參考資料給的參數上限2.8V下限1.2V略有不同。

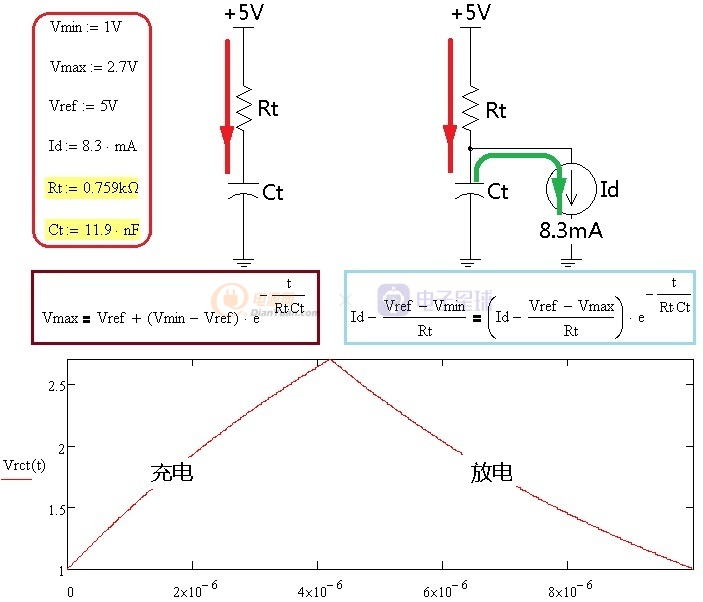

等效工作過程、波形及基本方程如下:

圖2 等效工作過程及基本方程

由圖2中的兩個基本方程經過整理可以得到不同特性曲線以便設計參考。

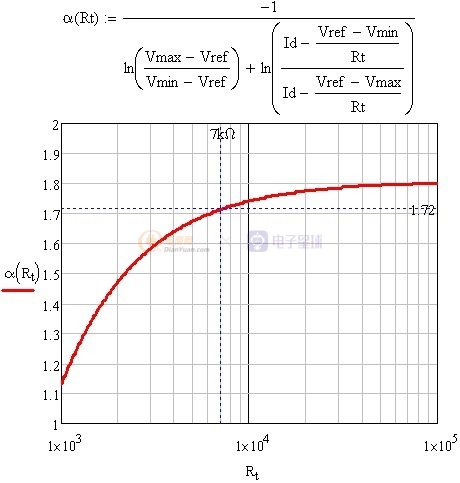

- 開關頻率設計

分別整理出充、放電公式,

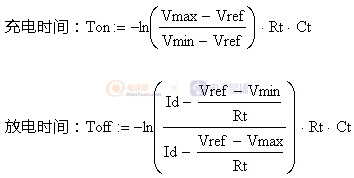

已知開關頻率fs=1/(Ton+Toff),再整理成fs=α/(Rt*Ct),其中系數α是電阻Rt的函數繪圖如下:

圖3 頻率系數與電阻Rt的關系

常見參考公式fs=1.72/(Rt*Ct)是在Rt=5kΩ下標定的(圖中由于參數偏差計算結果為7kΩ),當Rt≠5kΩ如圖所示系數要略做修正。

造成偏差的原因在圖2放電階段,除了恒流源Id放電外電容還會通過Rt充電,當Rt變小充電電流變大時帶來的影響就不可忽略了。

- 電阻Rt的設計參考

資料中會給出這樣一個圖:

圖4 死區時間與Ct電容

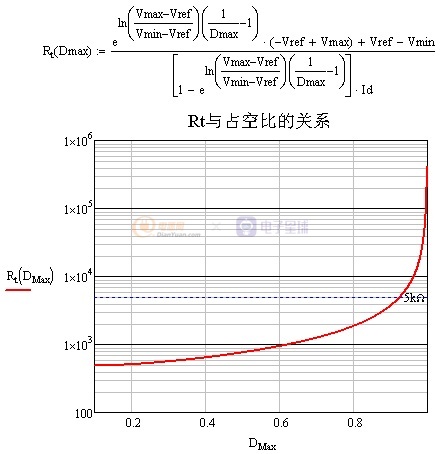

這里的死區時間也就是圖2中的放電時間(Toff),這段時間內PWM無輸出因而可以通過調節Toff時間來調節最大占空比Dmax,由公式Dmax=Ton/(Ton+Toff)整理后得Dmax只與電阻Rt有關,繪圖如下:

圖5 電阻Rt的設計參考

圖5就為電阻Rt的設計參考,例如想要限制最大占空比Dmax≈0.6時取Rt=1kΩ而與開關頻率及電容都無關。

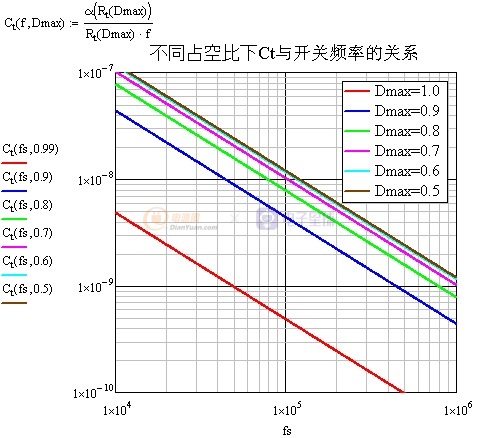

- 電容Ct的設計參考

前面已經獲得了頻率系數及電阻方程,頻率方程變換后既可得電容Ct=α/(Rt*fs),繪圖如下:

圖6 不同占空比下電容Ct與頻率的關系

上圖6為恒定不變所以參考此圖也可利用查表法選擇電容Ct。

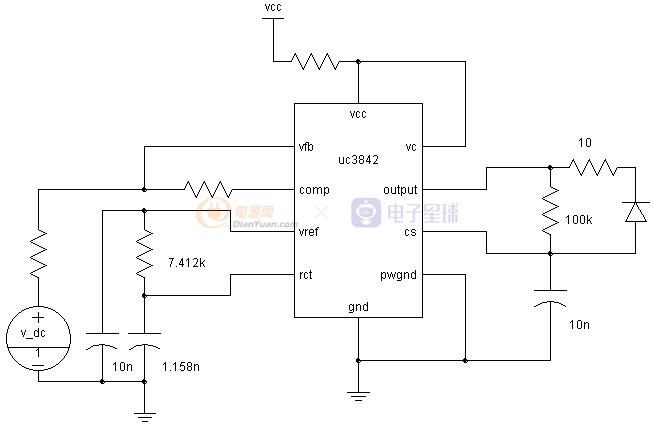

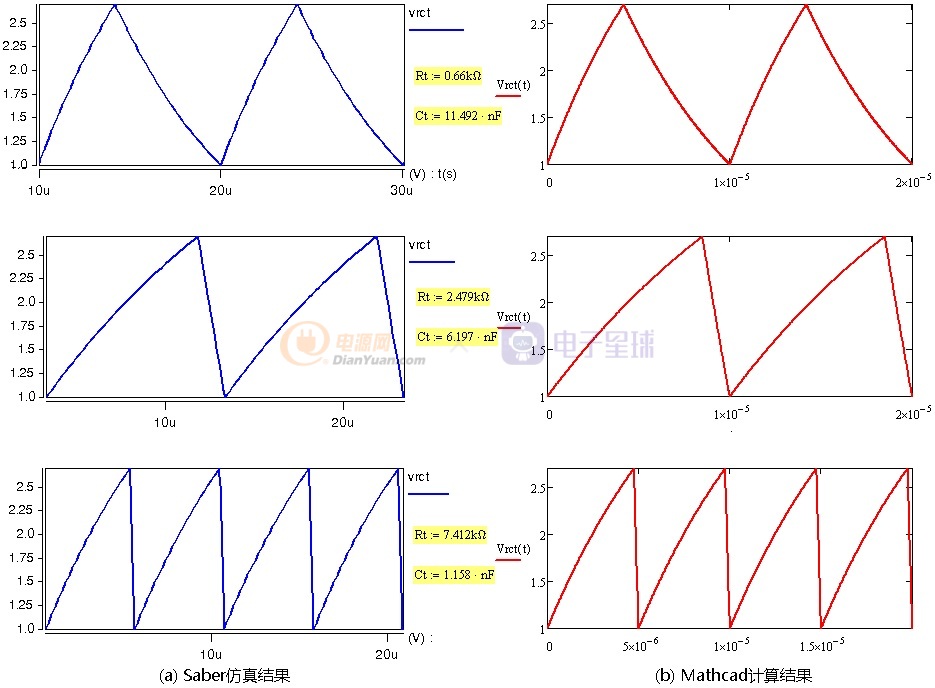

最后列舉幾組參數用Saber軟件進行對比驗證如下:

圖7 UC3842開關頻率仿真電路

圖8 Saber仿真與Mathcad公式計算對比

通過圖7的波形對比驗證了公式及電路模型基本是準確的,波形特性也基本可知,后續可以利用這個模型進行斜坡補償方面的驗算。