大家好,我是廣元兄。很高興和大家分享信號完整性的相關知識。希望大家點贊,分享。有什么問題加微交流學習,微信號【SI_Basic】。

Slogan:一起學習,共同進步!

芯片的納米工藝,大家可能不熟悉。但說到手機處理器應該不陌生,現有手機芯片一般用的是7納米工藝,網上說三星在瞄準3納米,而臺積電在布局4納米。這說明芯片溝道會越來越按比例縮小,集成電路的核心電壓會降低。但是功率和頻率卻在提升,這對于電源完整性未來的挑戰會越來越大。

說到電源完整性,先不說電源復雜的互連系統,單電源分配網絡(PDN)部分在產品設計中就需要足夠關注。

01

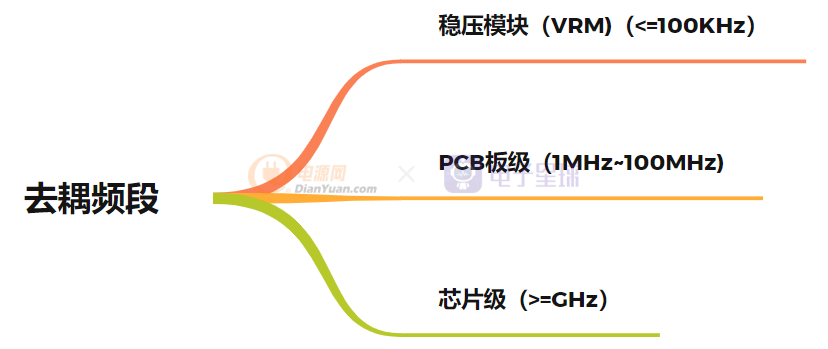

電源分配網絡包含從源端穩壓模塊(VRM)到芯片,芯片分配電壓,再到電源路徑(單層直達或過孔轉換的幾個層面),最終流向使用芯片或終端設備。

電源路徑與信號路徑是有區別的,電源分配網絡中一個電源路徑可以在一個節點分成多個路徑,或者說轉換成多個電源,終端掛多個元器件,可以理解為一對多。而信號路徑只能一對一。

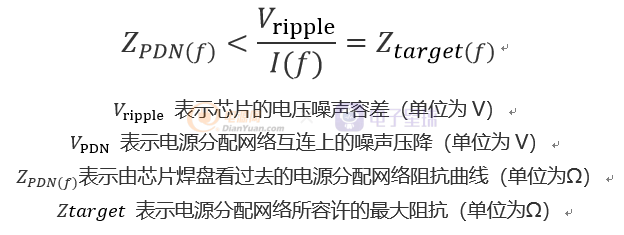

既然電源分配網絡是為終端設備提供所需電源,那就是有要求,就需要對電源分配網絡管控。路徑上電壓是有變化的,那么電源分配網絡的電流就會有波動,在這種情況下,就需要保持電源分配網絡阻抗低于目標阻抗。

目標阻抗的管控說到底就是路徑管控。兩個因素:電源和地平面之間介質盡量薄,盡量短而寬的走線。

02

下圖為消費類產品設計電源部分的實際情況圖:

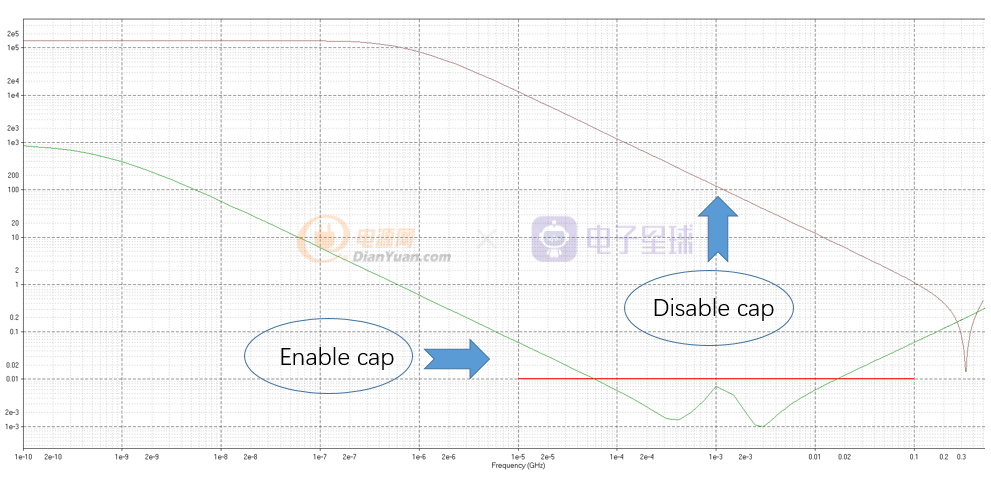

板級電源分配網絡設計的頻率范圍約從 1MHz 到 100 MHz。這正是電路板平面和多層陶瓷貼片電容器( MLCC) 發揮作用的頻率范圍 。這也是仿真時,重點關注的頻率范圍。

簡單來說,低頻率段由穩壓模塊來平衡,高頻率段由芯片片選電容來解決,中間的頻段就是板級來管控。

我們說的PDN設計一般就是指在PCB板級上給電源提供低阻抗路徑。這里面還有電容擺放位置、電容不同容值&個數、反諧振等方面,到仿真這一邊,就是交流部分:PDN阻抗提取和直流部分:IR Drop壓降。

03

當交流電流通過電源路徑時,電源分配網絡上也將產生電壓降,這個壓降會隨著頻率發生變化。電源路徑的不同(層數&Shape寬度等),造成的壓降變化是不同的,輸出穩定電壓到終端的難度很大,我們所要做的只是保證電壓的變化在一定的范圍之內,也就是所謂的噪聲容差。上式就可能轉換為目標阻抗:

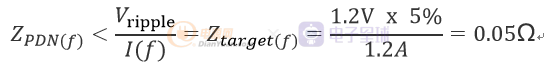

PCB板級PDN設計,需要先確定板級電源分配網絡的設計目標阻抗。舉例:1.2V的CPU用電為例,紋波百分比5%,最大電流為1.2A,根據公式:

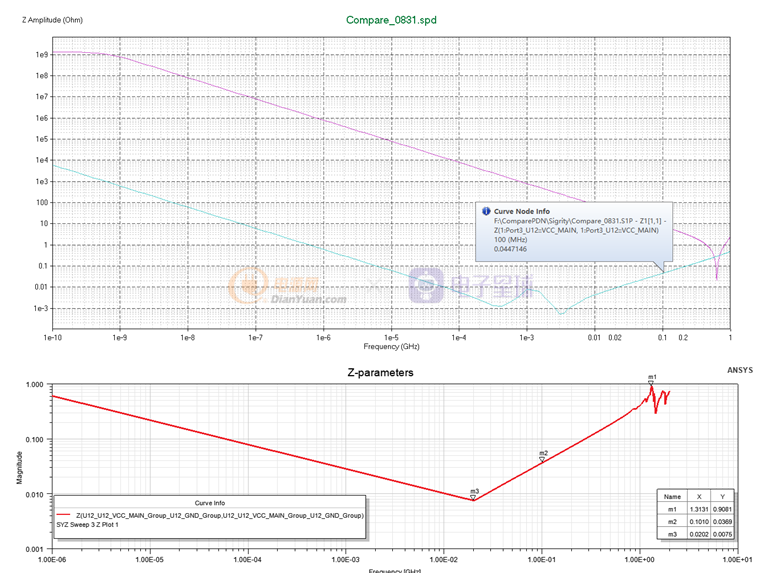

上圖說明,是否使能電容對PDN阻抗的影響很大。

04

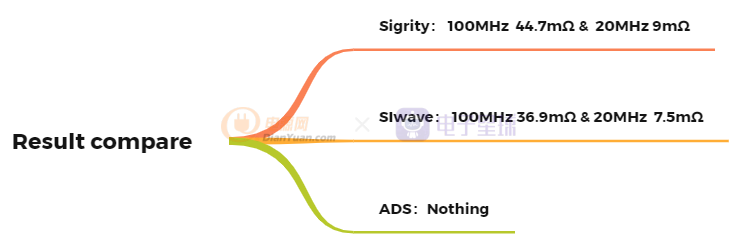

三個軟件的操作上來看,Sigrity&SIwave操作方式比較簡單,和寄生參數的提取大體相當。

Sigrity電容模型

只是容值模型部分需要關注與研究,特別針對實際產品設計和優化。

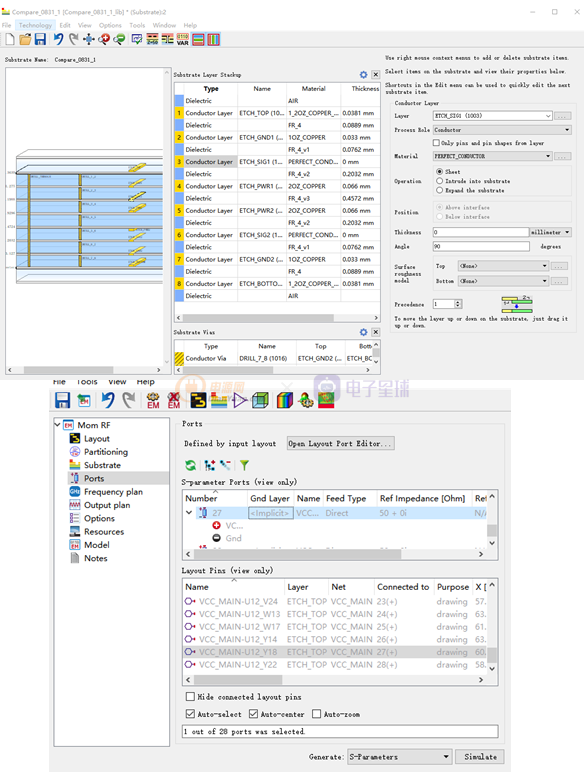

或許是不常用也或許是其他原因,ADS上操作相對比較麻煩,花費的時間也比較長,這個時間是指EM仿真時間(30分鐘以上)。不知道ADS新的版本或者操作上有沒有更新改善。

反正這一通下來,感覺就是:一頓操作猛如虎,看到結果心里苦。最終,放棄了。

看到S參數就知道有問題。感覺應該是在疊層設置或者端口的設置那邊出了問題。

疊層的部分,負片層方向;

端口的部分,Port負端方向。

三個軟件操作步驟:

PDN提取的的時候,ADS軟件給出頻率掃描范圍的建議,最高500MHz。

仿真出的結果對比: