說到環(huán)路,我相信對于電源工程師來說都是個頭疼的問題。經(jīng)常會有初學(xué)者在設(shè)計(jì)一款電源后調(diào)試,發(fā)現(xiàn)波形雜亂,還伴隨著花里胡哨的震蕩,卻又無從下手,環(huán)路理論涉及的知識比較廣。確實(shí)不是看一篇兩篇文章就能搞懂的,因此我開設(shè)一個小專題,專門來研究研究環(huán)路。

我們不從繁瑣的環(huán)路理論知識去學(xué)習(xí)和認(rèn)知環(huán)路,而是通過一個實(shí)際案例來分析關(guān)于環(huán)路的方方面面。

開篇,我舉一個開關(guān)電源調(diào)試過程中會碰到的一個常見的問題:

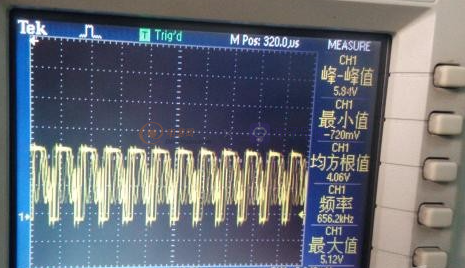

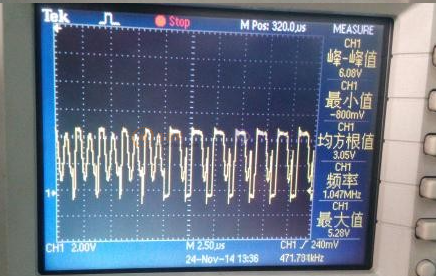

我們在調(diào)試的時候,可能會遇到波形劇烈抖動,且無規(guī)律,可能還伴隨著大小波的情況。遇到這種現(xiàn)象那么我們就要考慮是不是我們的環(huán)路設(shè)計(jì)出現(xiàn)了問題。

一、反激介紹--穩(wěn)壓電源是如何工作的?

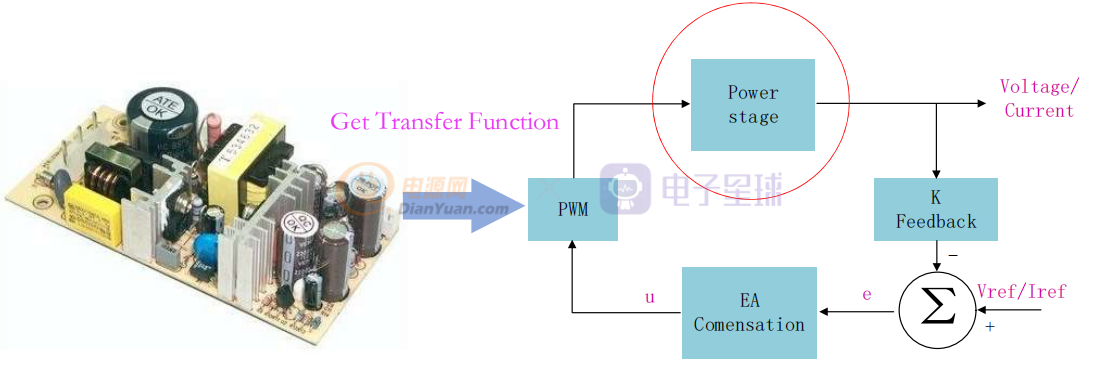

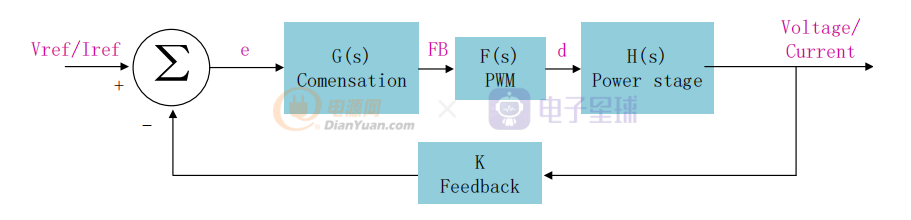

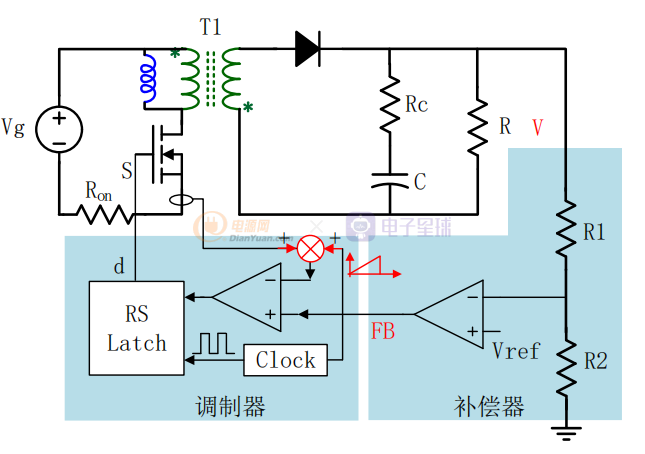

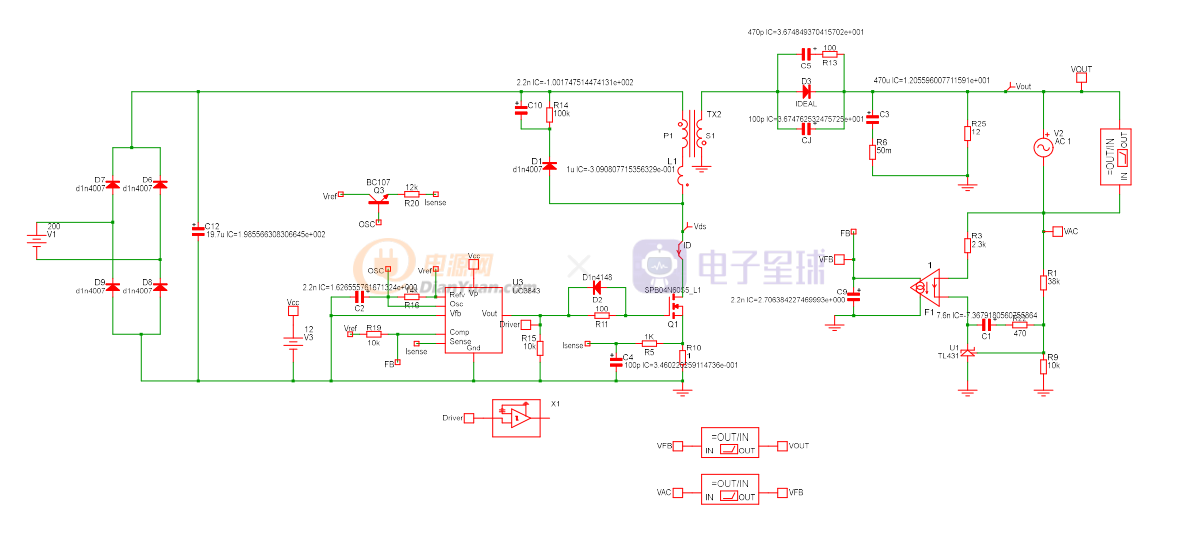

從圖中我們可以看出,一個開關(guān)電源是有功率級+調(diào)制器+補(bǔ)償器組成的。我們前面有分析過反激變換器的工作原理以及計(jì)算,在這里進(jìn)行一個小總結(jié):

1、Vout 每時每刻參考 Vref 進(jìn)行比較以獲得誤差 ?= Vref –k*Vout 。

2、誤差補(bǔ)償?shù)玫娇刂菩盘枴?/p>

3、調(diào)制器將控制信號轉(zhuǎn)移到 PWM。

4、功率級做出反應(yīng)以盡可能地減小 ?。

經(jīng)過上述過程,我們就能理解反激變換器在閉環(huán)控制時的工作過程。

那么,客戶想要一個啥樣的電源呢?

1、穩(wěn)定--無論負(fù)載、輸入、溫度和其他條件如何。

2、精準(zhǔn)--輸出就是我們想要的。

3、快速--對任何傳入擾動(例如負(fù)載瞬變)的快速反應(yīng)。

二、反激穩(wěn)態(tài)--什么是極點(diǎn)、零點(diǎn)和bode圖?

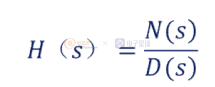

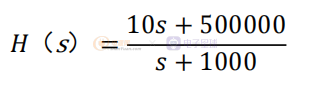

概念我就不在這啰嗦了,后續(xù)我們會逐一討論。先來看看,對于一個電路開環(huán)的傳遞函數(shù)是啥樣的:

求解 N(s)=0 得到零,求解 D(s)=0 得到極點(diǎn)。舉個栗子:

我們分別令分子、分母=0,可以得到:

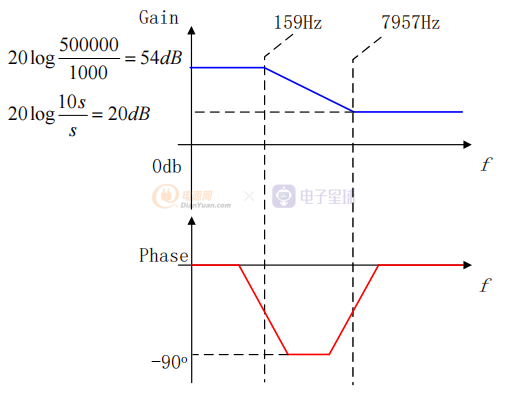

根據(jù)以上式子我們可以畫出響應(yīng)的bode圖,也就是增益和相位:

實(shí)際中,我們得到的不是這種圖像,而是平滑曲線。

了解了相關(guān)傳遞函數(shù),我們就來分析震蕩是怎么產(chǎn)生的,我們?nèi)绾稳ケ苊庹鹗帲?/strong>

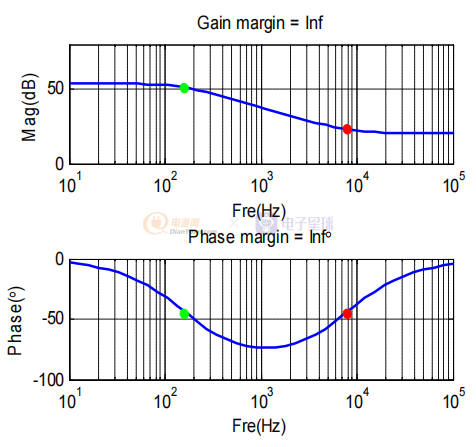

我們先來看看反激的閉環(huán)系統(tǒng)是長啥樣的:

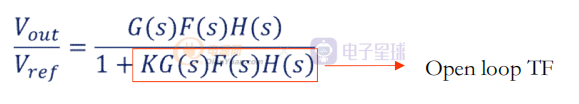

前面我們小結(jié)了一波反激變換器的閉環(huán)工作方式,我們在這里直接用方框圖來說明。K:反饋,G(s):補(bǔ)償,F(xiàn)(s):PWM控制器,H(s):功率級。由此我們可以寫出,該閉環(huán)控制環(huán)路的傳遞函數(shù):

從中我們可以看到,KG(s)F(s)H(s)是一個開環(huán)的傳遞函數(shù),如果出現(xiàn)分母為零,那么該等式就無解,也就是說系統(tǒng)永遠(yuǎn)也不會穩(wěn)定,就會出現(xiàn)自激振蕩的現(xiàn)象:

但是,一般我們實(shí)際測試過程中,用的最多的是環(huán)路分析儀,這些等式只是在理論分析的過程中才會用到,那么實(shí)際我們通過環(huán)路分析儀測試出來的bode圖如何去判斷系統(tǒng)是否穩(wěn)定呢?

我們首先要了解,環(huán)路分析儀出來后,有一個相位phase和一個增益gain,我們怎么去看。

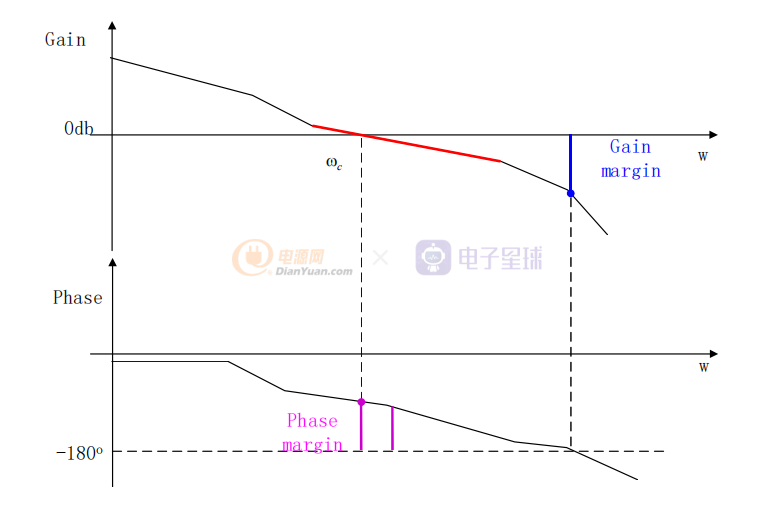

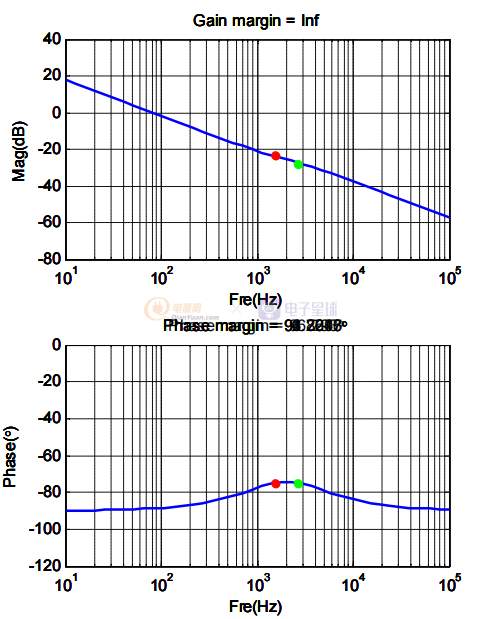

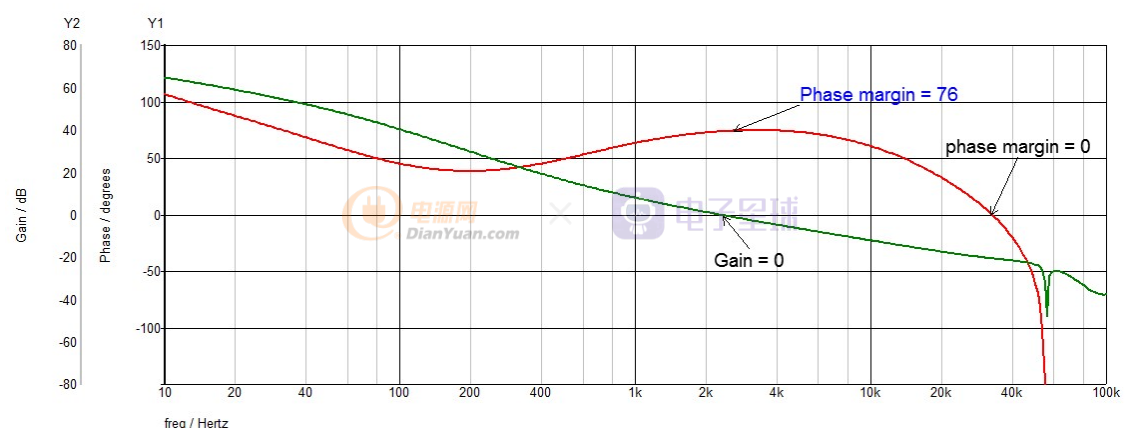

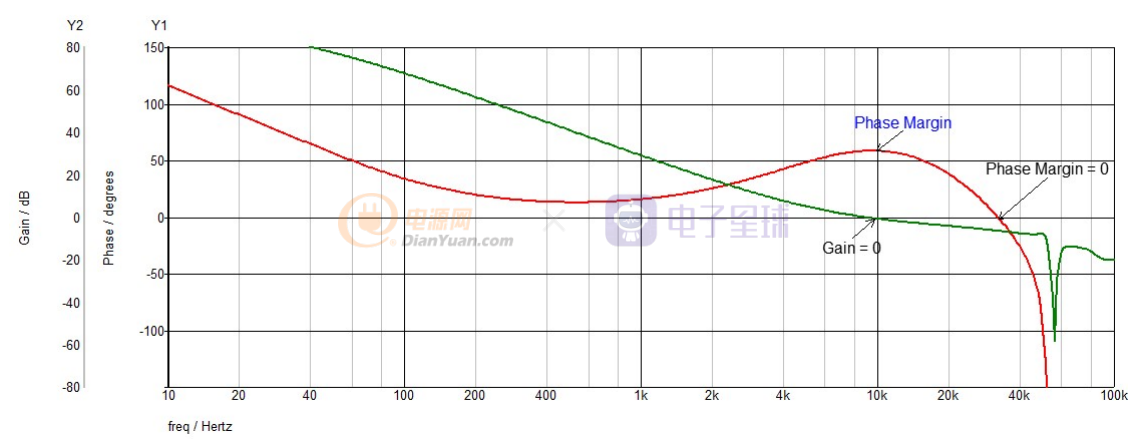

一般而言,測試出來橫坐標(biāo)都是頻率的十倍頻,雙坐標(biāo)系中有dB單位的是對應(yīng)的增益,以多少°對應(yīng)的是相位。從圖中我們可以得到啥呢?首先是增益的過零點(diǎn)處,所對應(yīng)的的橫坐標(biāo)我們叫穿越頻率,增益過零點(diǎn)處對應(yīng)的相位與180°的差值的絕對值為相位裕度,相位過180°處所對應(yīng)的增益與0dB的差值的絕對值是增益余量。

知道這寫bode圖上的信息后,我們還需要了解這些穿越頻率、相位裕度、增益余量到低多少合適?

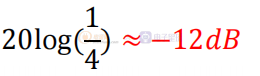

對于增益余量,我們希望每個周期的單次噪聲都可以衰減到1/4,即:

我們通過圖中可以了解到:

1)Q 因子為 0.5(臨界響應(yīng))意味著相位裕度為 76°

2)45°的相位裕度對應(yīng)于 1.2 的 Q:振蕩響應(yīng)!

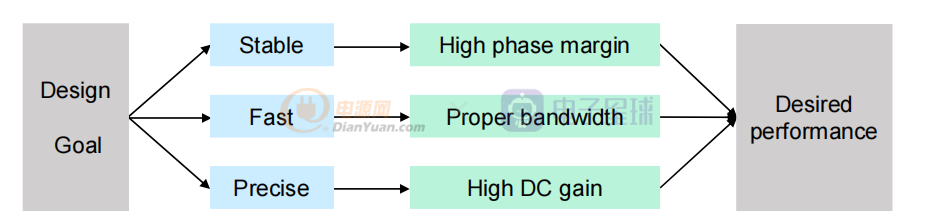

了解了以上信息,到底啥樣的bode圖是我們所需要的呢?

總結(jié)一下:

穩(wěn)定--較高的相位裕度

快速--合適的帶寬(即穿越頻率)

精準(zhǔn)--高直流增益

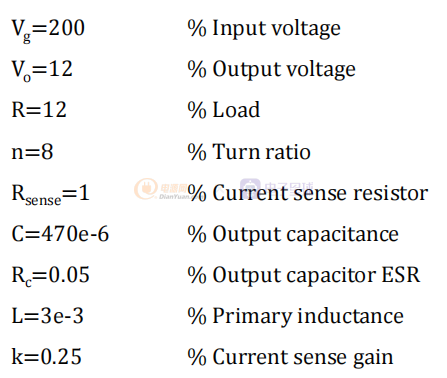

其實(shí),這些圖像我們在分析的時候可以用mathcad去畫出來的,首先我們需要算出反激的傳遞函數(shù),舉個栗子:

要去畫出系統(tǒng)的小信號模型,其次針對反饋、控制器、功率級進(jìn)行重點(diǎn)拆分,即影響環(huán)路的器件,最后就能列出表達(dá)式:

這個怎么寫出來的,后面我們也會一一講到。接下來我們就可以根據(jù)等式代入已知量:

三、補(bǔ)償環(huán)路設(shè)計(jì)

在設(shè)計(jì)之前我們要了解,補(bǔ)償器的基本原型:

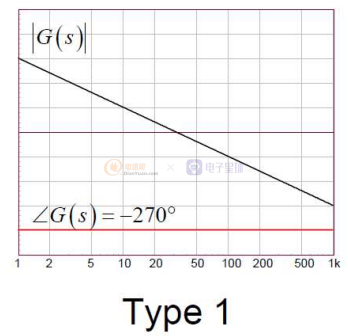

1、Type1:1極點(diǎn)在原點(diǎn),無相位提升

2、Type2:原點(diǎn)1極點(diǎn),1零1極,相位提升至90°

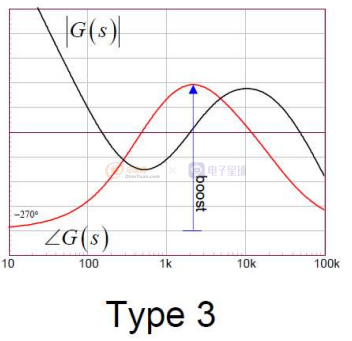

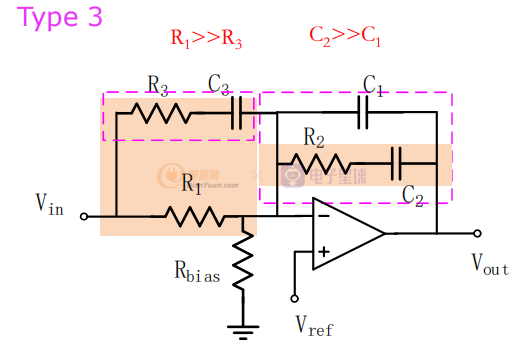

3、Type3:原點(diǎn)1極點(diǎn),2零2極,相位提升至180°

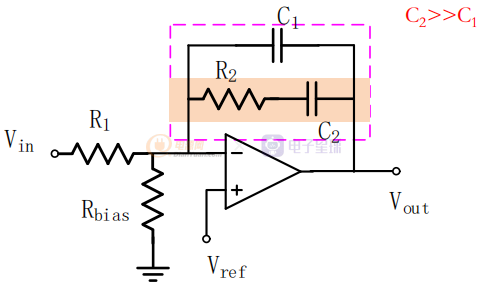

我們在反激變換器中,常用的是TYPE2,所以針對type2我們著重講解一下。首先為了直觀的反應(yīng)補(bǔ)償機(jī)理,我們用運(yùn)放來進(jìn)行分析。

根據(jù)運(yùn)放的虛短虛斷,我們可以得到傳遞函數(shù):

由于C2遠(yuǎn)大于C1,我們假若沒有C1可以得到:

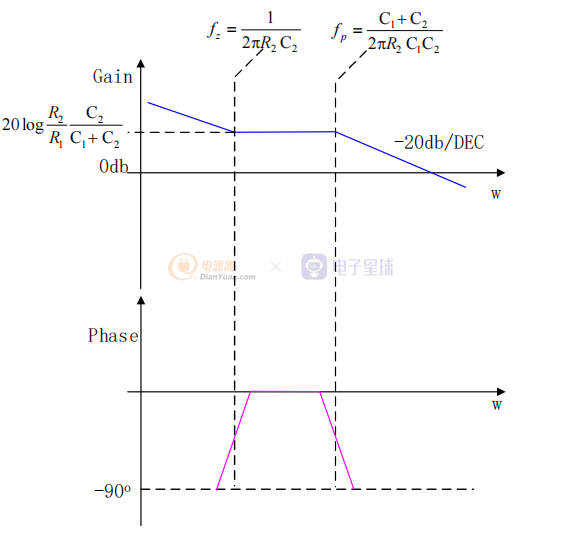

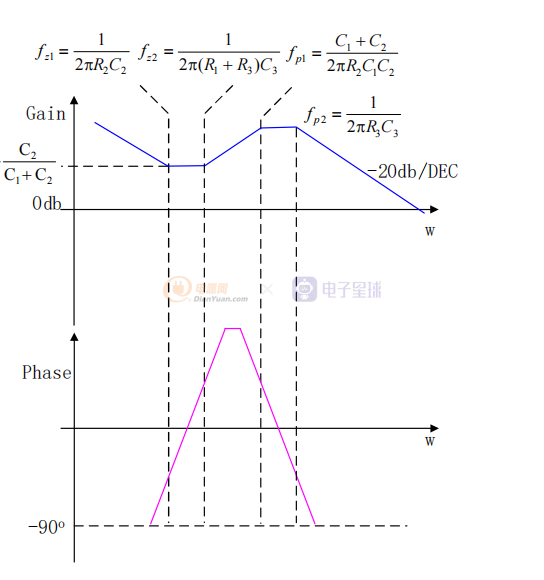

根據(jù)前面章節(jié)提到的算法,我們可以畫出type2的bode圖:

也就反映出,這種補(bǔ)償電路在環(huán)路中的補(bǔ)償形式。具體來看電容在環(huán)路增益中起到了哪些作用呢?

首先是C1,我們假設(shè)從1nF變化到30nF:

我們可以發(fā)現(xiàn)隨著C1電容的增大,零極點(diǎn)之間的平臺越來越窄,最終增益變成一條近似線性的曲線。

而在type3中呢,雖然不常用,但是也要看看type3的變化趨勢。

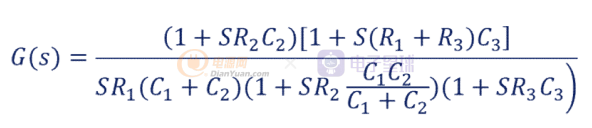

同理可以得出傳遞函數(shù):

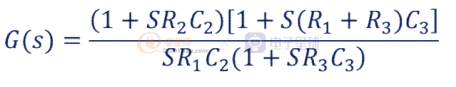

假設(shè)C1忽略掉,我們可以得出:

畫出該傳遞函數(shù)的bode圖:

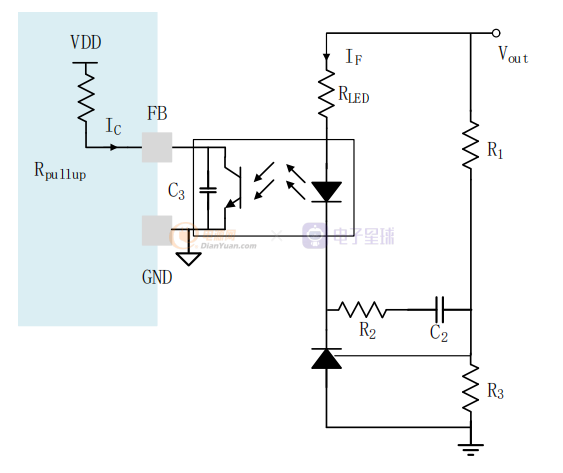

以上我們是針對type2、type3典型運(yùn)放進(jìn)行分析,在實(shí)際電路中我們用的是TL431和光耦構(gòu)成的反饋電路,那我們怎么去分析,去寫出正確的傳遞函數(shù)進(jìn)行分析呢?

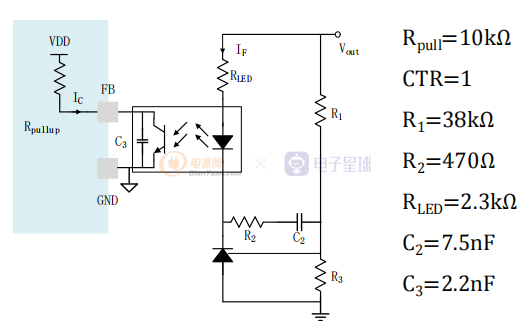

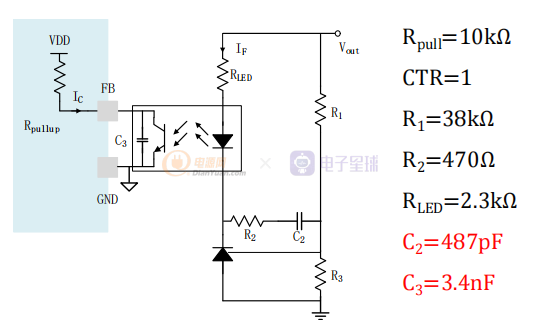

實(shí)際的反饋環(huán)路如圖

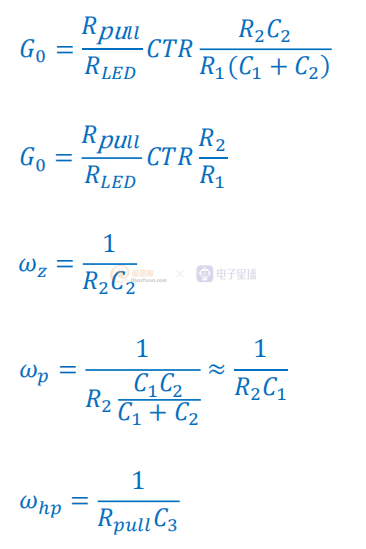

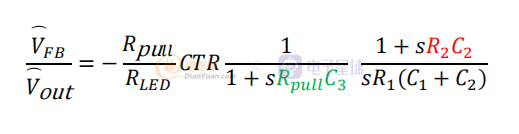

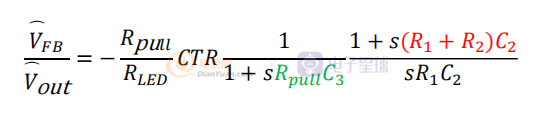

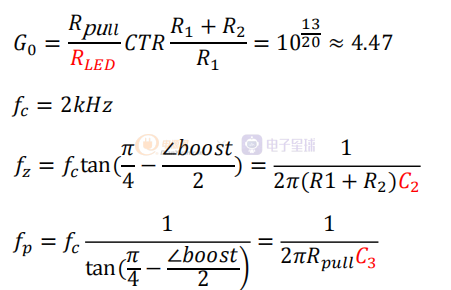

我們要寫出其環(huán)路的傳遞函數(shù):

從表達(dá)式我們可以得出:

假設(shè)沒有C1:

我們的傳遞函數(shù)為:

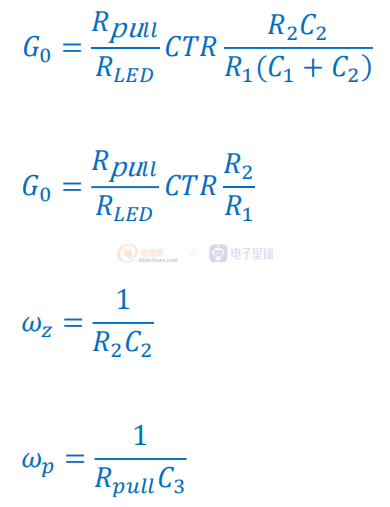

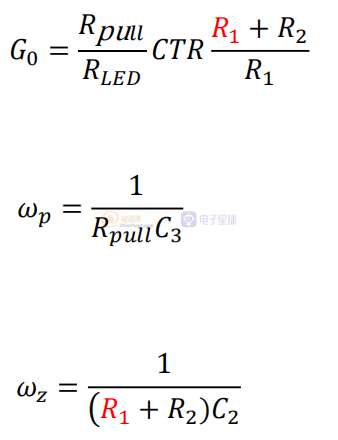

令分子、分母為零,可以得出:

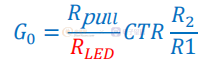

看到等式后,我們需要了解每個器件的值會影響系統(tǒng)哪些參數(shù),首先我們需要知道,增益的變化由啥參數(shù)決定?

舉個栗子,系統(tǒng)有如下參數(shù):

R1=38kΩ;

R2=10kΩ;

C2=22nF;

C3=1nF;

Rpull=39kΩ;

CTR=1;

Rled=5.1kΩ;

通過我們解得的傳遞函數(shù),零極點(diǎn)情況:

我們可以清晰的發(fā)現(xiàn),改變Rled這個電阻可以改變環(huán)路的增益,具體的用波形來反應(yīng):

我將Rled電阻阻值從5.1k變到2.2k,1k,510Ω

我們可以看到,增益曲線往上平移,由此增大Rled能夠有效增大穿越頻率。

如果我們調(diào)整R2,會發(fā)生啥變化呢?我們將R2從10k變化到22k、47k、100k,同時變化C2:10nF、4.7nF、2.2nF,可以得到:

從圖上可以看出,增益往下平移,穿越頻率減小,相位裕度增大。

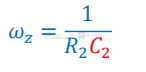

如何改變零點(diǎn)?根據(jù)表達(dá)式:

我們可以改變C2,來改變零點(diǎn):C2 22nF、47nF、100nF、220nF

我們也可以改變R2來改變零點(diǎn):R2=10k、22k、47k、100k 為了不影響增益,此時R1的值=83.6k、178.6k、380k

如何改變極點(diǎn)?有表達(dá)式:

C3可以改變系統(tǒng)的極點(diǎn),C3=1nF、470pF、220pF、100pF

那我們工程師在設(shè)計(jì)電路時,如何先去預(yù)選一些參數(shù)呢?

首先我們要根據(jù)電路圖,選取關(guān)鍵元器件去計(jì)算

傳遞函數(shù)如下:

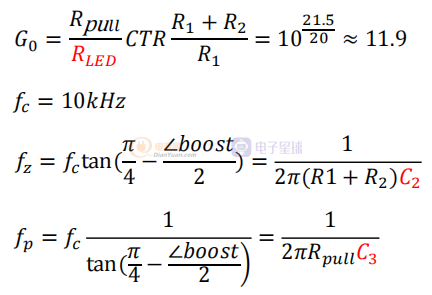

擺式子,列方程:

假若我們手頭沒有環(huán)路分析儀,我們怎么粗略畫出bode圖:

假設(shè)我們設(shè)置的穿越頻率是1khz,我們就能得出零極點(diǎn)的頻率點(diǎn):

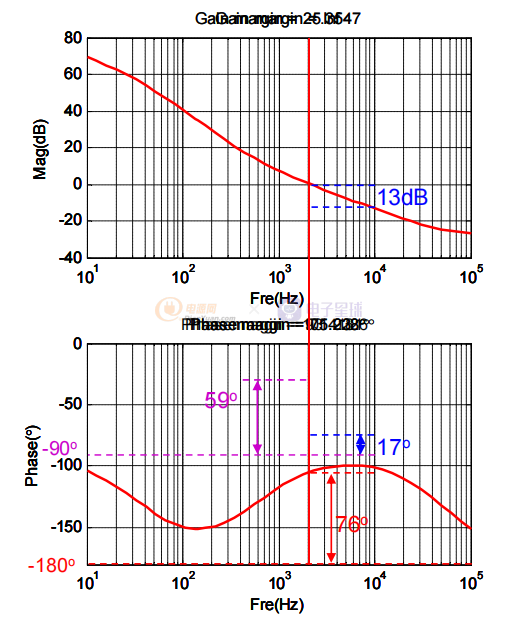

為了直觀展示,舉個栗子:

eg1:設(shè)計(jì)一個帶寬bandwidth=2kHz,相位裕量Phase margin=76°的系統(tǒng)

那我們就開始套公式:

那么可以得出零極點(diǎn)的頻率,就能算出各個元器件的具體值:

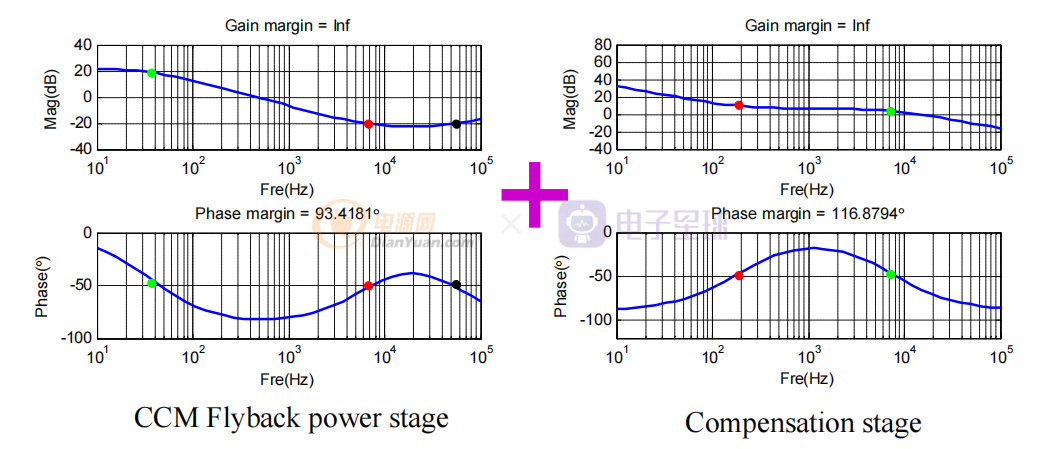

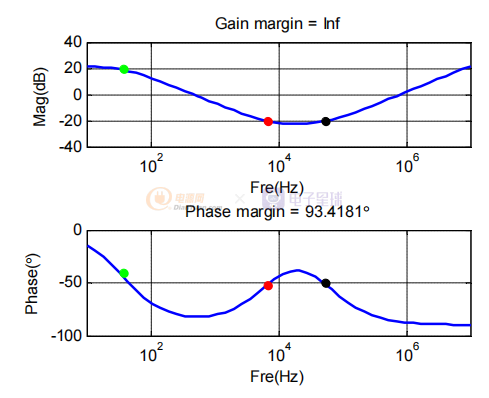

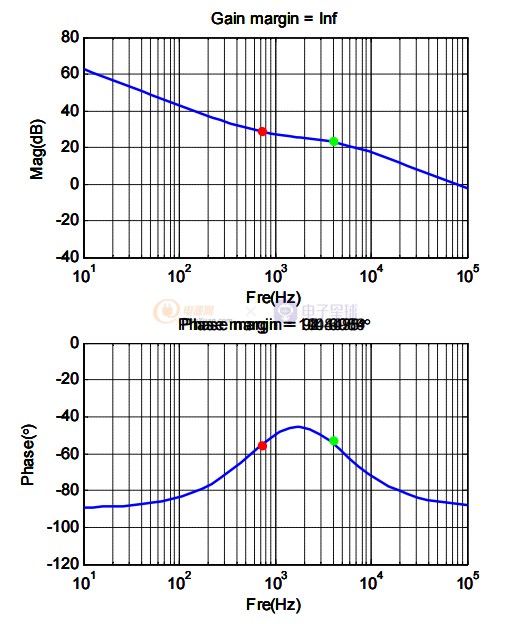

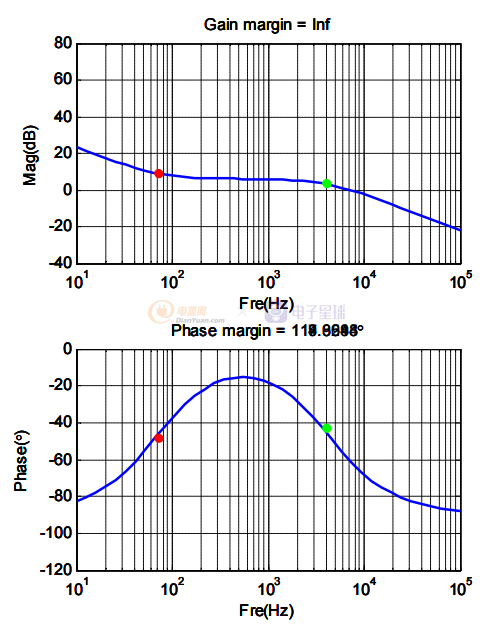

我們通過仿真來校驗(yàn)一下,是騾子是馬拉出來溜溜:

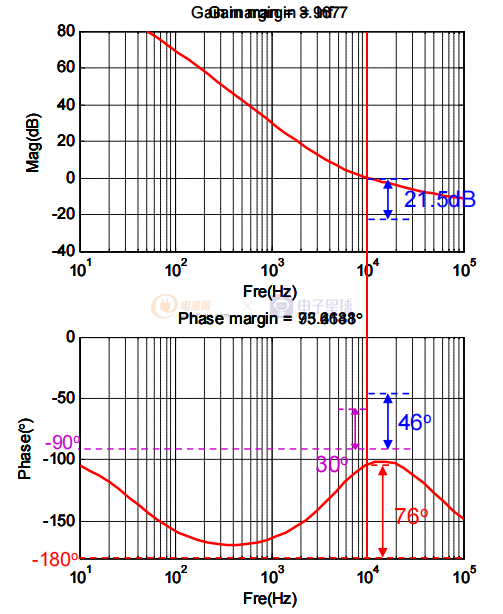

仿真結(jié)果如下:

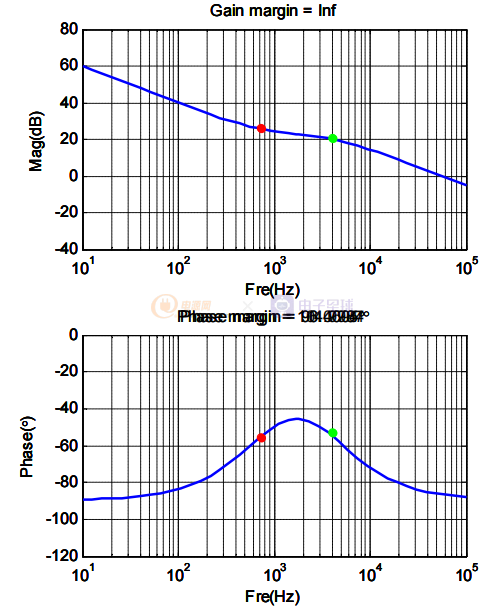

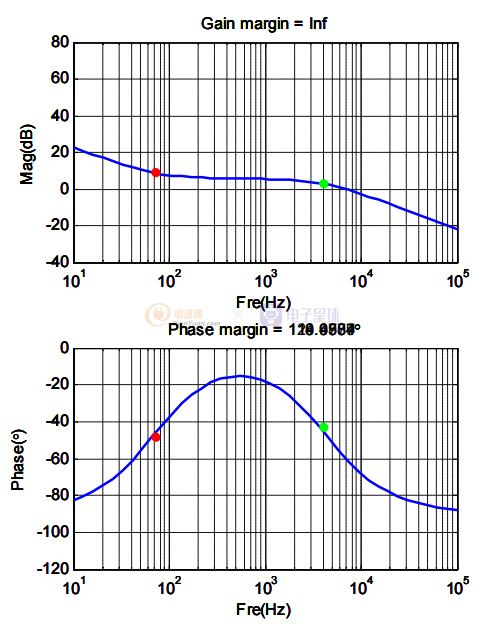

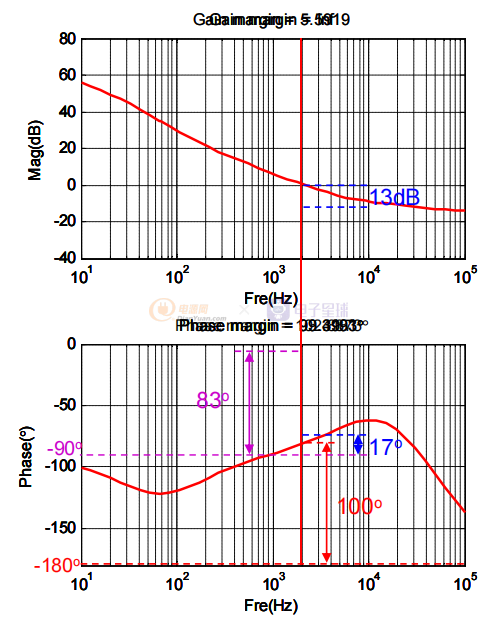

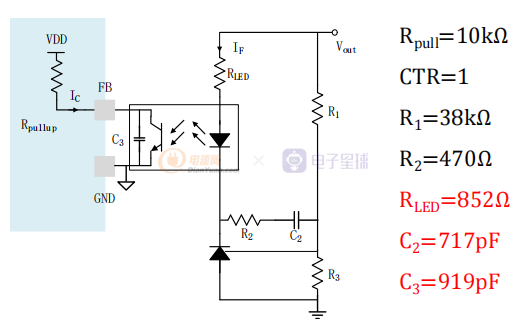

eg2:設(shè)計(jì)一個帶寬bandwidth=2kHz,相位裕量Phase margin=100°的系統(tǒng)

關(guān)鍵元器件參數(shù):

仿真結(jié)果如下:

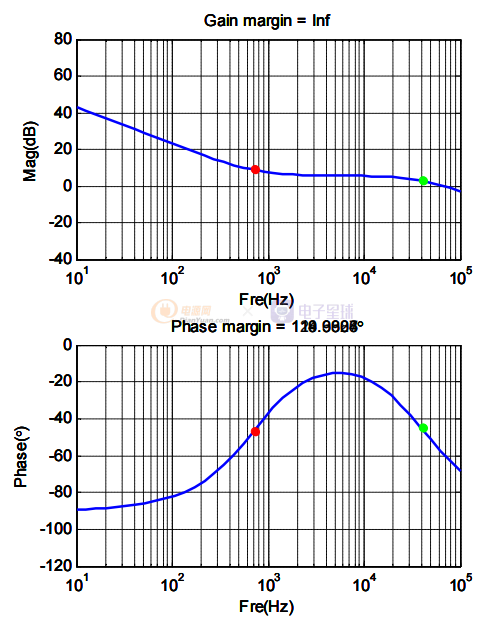

eg3:設(shè)計(jì)一個帶寬bandwidth=10kHz,相位裕量Phase margin=76°的系統(tǒng)

我們可以得到相關(guān)元器件參數(shù):

仿真結(jié)果如下:

實(shí)際中環(huán)路測試接線圖如下:

兩端電阻可以選擇10Ω或者51Ω,主要是為了與環(huán)路分析儀的阻抗進(jìn)行匹配。

這篇文章主要是通過一個實(shí)際例子來分析環(huán)路的要點(diǎn),如果對你的設(shè)計(jì)或者調(diào)試有幫助,那請為我一鍵三連吧,有問題的話可以在評論區(qū)留言,謝謝。文末有仿真源文件,歡迎下載!