LUT、分布式RAM和SR

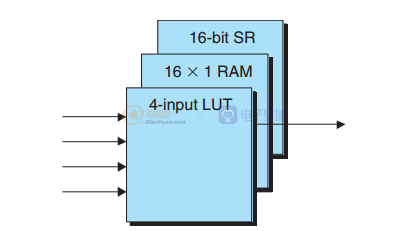

基于SRAM的設(shè)備中LUT的核心由許多SRAM單元組成,除了作為查找表的主要功能外,一些供應(yīng)商還允許構(gòu)成LUT的單元用作一小塊RAM。

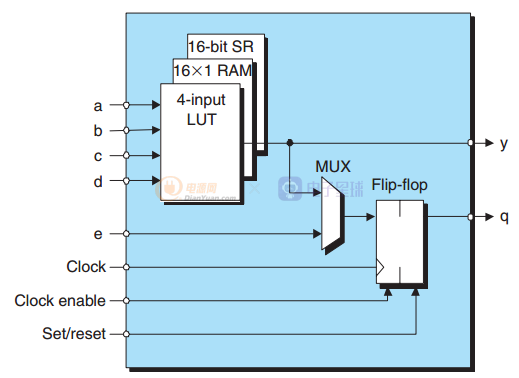

再深入可編程的Logic cell。可編程邏輯塊將包含其他元素,如多路復(fù)用器和寄存器。例如賽靈思的邏輯單元:

邏輯單元

首先,不同的FPGA供應(yīng)商,對于邏輯單元有著不同的稱呼。需要在查閱其規(guī)格書時分辨。例如,Xilinx的FPGA中的核心構(gòu)建塊稱為邏輯單元 logic cell (LC)。

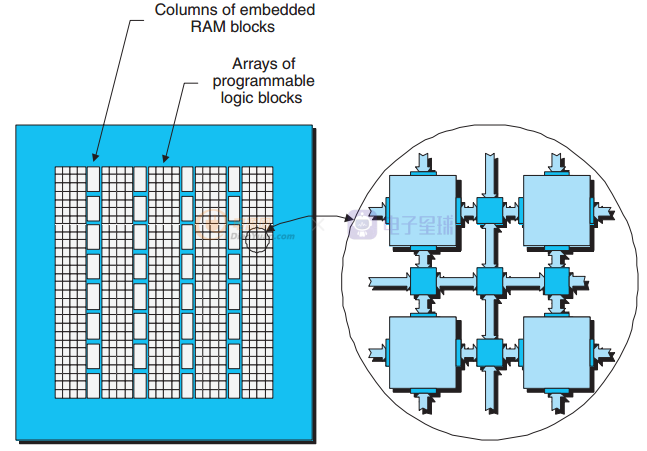

內(nèi)嵌RAM

許多應(yīng)用程序需要使用內(nèi)存,因此fpga現(xiàn)在包括了相對較大的嵌入式RAM塊,稱為e-RAM或塊RAM。 根據(jù)組件的架構(gòu),這些塊可能被放置在設(shè)備的外圍,分散在相對隔離的芯片表面,或被組織成柱狀。

根據(jù)器件的不同,這樣的RAM可以容納幾千到幾萬位比特。此外,一個器件可能包含數(shù)十到數(shù)百個這樣的RAM塊,因此提供了從幾十萬位到幾百萬位的總存儲容量。每個RAM塊可以單獨使用,或者多個塊可以組合在一起實現(xiàn)更大的塊。這些塊可以用于各種目的,例如實現(xiàn)標(biāo)準(zhǔn)的單端口或雙端口ram、先進先出(FIFO)函數(shù)、狀態(tài)機等等。

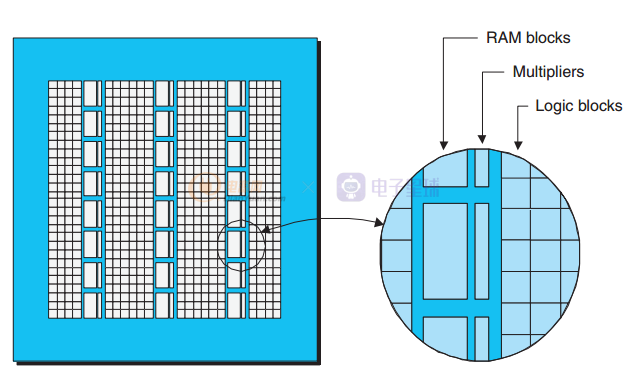

嵌入式乘法器、加法器等

一些函數(shù),如乘數(shù),如果它們是通過連接大量可編程邏輯塊來實現(xiàn)的,那么其運行速度會受限制。由于許多應(yīng)用需要這些功能,許多fpga集成了特殊的硬接線乘法器塊。乘法器塊通常會分布在RAM旁,以便于快速地讀寫數(shù)據(jù)。同樣的,加法器也是如此。現(xiàn)在的FPGA都會集成這些功能塊,以便于功能運行速度更加地快捷。

嵌入式處理器核心

大家需要知道這樣的一個事實,在電子嵌入式的領(lǐng)域中,軟硬不分家。通常的,一些FPGA能實現(xiàn)的功能,也能有微處理器、微控制器完成。兩者之間的區(qū)別就是,運行速度的快慢。

1、對于運行時間嚴格的,ps或者ns級別的邏輯實現(xiàn),必須由FPGA實現(xiàn)。

2、微妙級別的功能運行速度要求的功能,兩者一般都可以實現(xiàn)。

3、毫秒級別的功能,例如讀取開關(guān)信號,點亮一個燈。這些功能一般都需要計數(shù)定時器去實現(xiàn)硬件級別的降速,因此,將這些任務(wù)作為微處理器代碼來實現(xiàn)通常更好。

通常來說,微控制器與FPGA是分立出現(xiàn)在一個功能上的。但是現(xiàn)在的高端FPGA,為了增強功能,都會集成進一個微控制器或微處理器。這提供了許多優(yōu)點,至少可以節(jié)省使用兩個設(shè)備的成本;它消除了電路板上的大量信號傳輸線路、過孔和引腳;而且它使板子更小更輕。

那么下一篇就繼續(xù)介紹嵌入式微核中的硬微核和軟微核的區(qū)別。