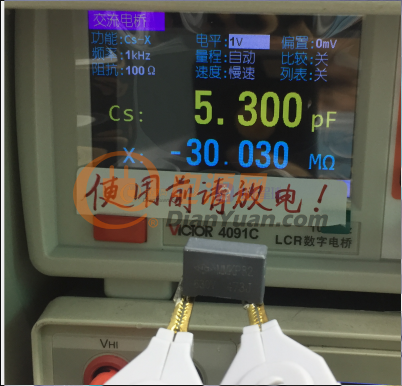

LLC拓樸中諧振電容容量由47nF受高溫鼓包變值為6PF,一通電即燒上下MOS管,三極都擊穿

LLC拓樸中諧振電容容量由47nF受高溫鼓包變值為6PF,一通電即燒上下MOS管,三極都擊穿,必須將此三個元件同時換掉才修好,請問為什么會燒上下管,原理是什么?芯片開關頻率FSW低于兩個諧振頻率FR1,FR2導致嗎?

全部回復(11)

正序查看

倒序查看

@lqh1972

[圖片]當功率降低,以及LLC電壓超過目標調節電壓(12V或是19.5V時),光耦上的電流會增長,同時SNSFB電壓降低,如上圖所示。諧振變換器會按照內部的頻率控制曲線升高頻率。因為頻率越高,輸出的功率也降低,輸出電壓也降低。如果輸出電壓變得很低很低,控制會降低系統工作頻率,增加系統輸出功率。通過這種方式,系統會將輸出功率調節到需求的大小。

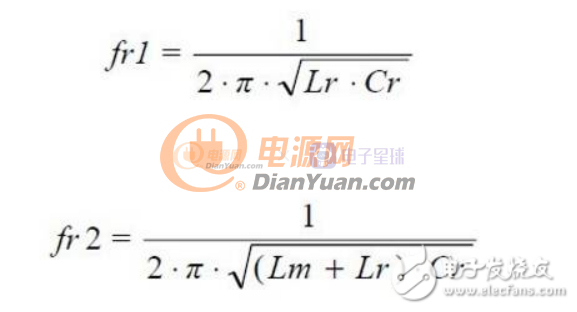

上式中為LLC拓樸兩個諧振頻率,FR1為重載時因負載的反射作用Lm短路未能與諧振,故諧振頻率要高,FR2空載時諧振頻率,勵磁電感Lm參與諧振,故諧振頻率會低。與PWM不同原理,當UO(P())↑→光耦1,2ILED↑→光耦3,4腳ICE↑→IC VFB↓→PWM IC內占空比D↓→開關MOS管導通時間會變短,變壓器初級儲能會變小,變壓器耦后反饋次級電壓會降低,→UO(P())↓從而達到穩壓的目的。而LLC PFM原理不能理解:當UO(P())↑→光耦1,2ILED↑→光耦3,4腳ICE↑→IC VFB↓→fSW↑芯片內諧振變換器會按照內部的頻率控制曲線升高開關頻率fSW→UO(P())↓(此步理解不了,因PFM開關導通時間不變tON , fSW上升則T反而是下降,T=1/ f,又因為T=tON+tOff ,開關管導通時間不變,周期下降則開關截止時間也變短,按理論應該是輸出電壓會上升才對,怎么會下降呢。

0

回復

@lqh1972

[圖片]上式中為LLC拓樸兩個諧振頻率,FR1為重載時因負載的反射作用Lm短路未能與諧振,故諧振頻率要高,FR2空載時諧振頻率,勵磁電感Lm參與諧振,故諧振頻率會低。與PWM不同原理,當UO(P())↑→光耦1,2ILED↑→光耦3,4腳ICE↑→ICVFB↓→PWMIC內占空比D↓→開關MOS管導通時間會變短,變壓器初級儲能會變小,變壓器耦后反饋次級電壓會降低,→UO(P())↓從而達到穩壓的目的。而LLCPFM原理不能理解:當UO(P())↑→光耦1,2ILED↑→光耦3,4腳ICE↑→ICVFB↓→fSW↑芯片內諧振變換器會按照內部的頻率控制曲線升高開關頻率fSW→UO(P())↓(此步理解不了,因PFM開關導通時間不變tON,fSW上升則T反而是下降,T=1/f,又因為T=tON+tOff ,開關管導通時間不變,周期下降則開關截止時間也變短,按理論應該是輸出電壓會上升才對,怎么會下降呢。

LLC PFM頻率調制,開關頻率FSW與兩個諧振頻率FR1,FR2一直搞不懂是怎么根椐輸出負載而變化的。輸出負載變化時FR1(空載或輕載時諧振頻率),FR2(重載時諧振頻率),FSW(芯片內開關工作頻率)都在隨負載變化,且要維持FR1>FSW>FR2,請大師指點迷津。

0

回復

@zq841102

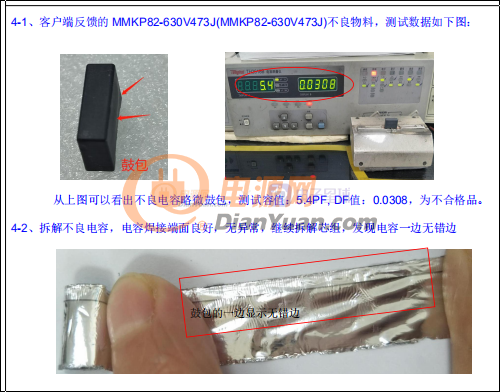

一看就是假貨。法拉的不是這種顏色的

/upload/community/2020/12/03/1606983243-81822.pdf 供應商回復報告為生產時沒有錯邊造成老化鼓包

0

回復