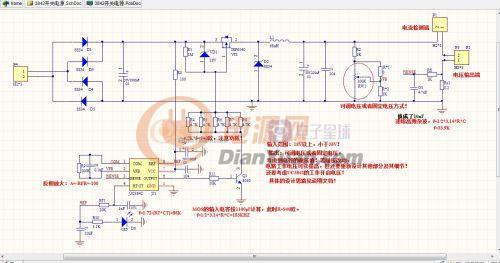

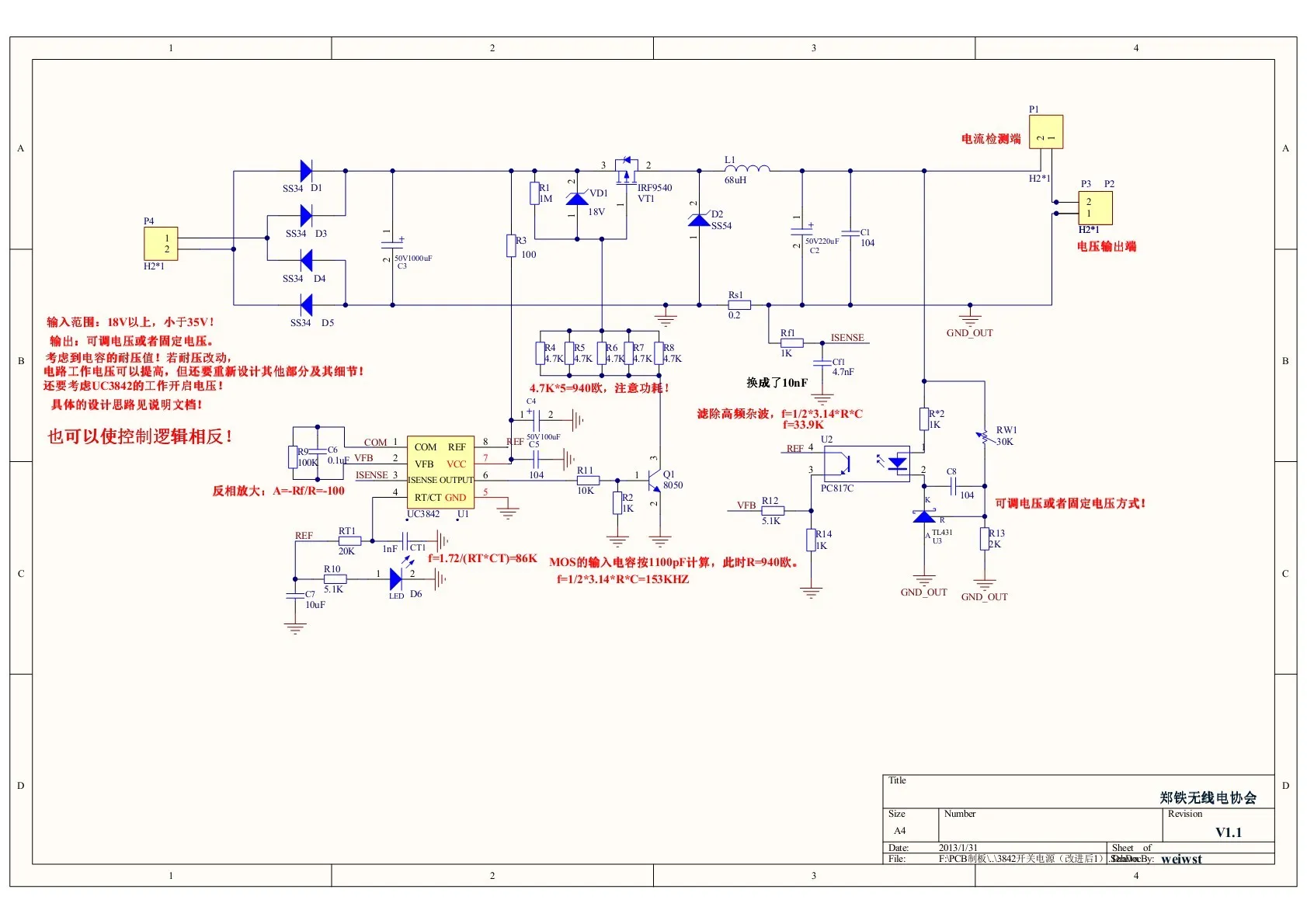

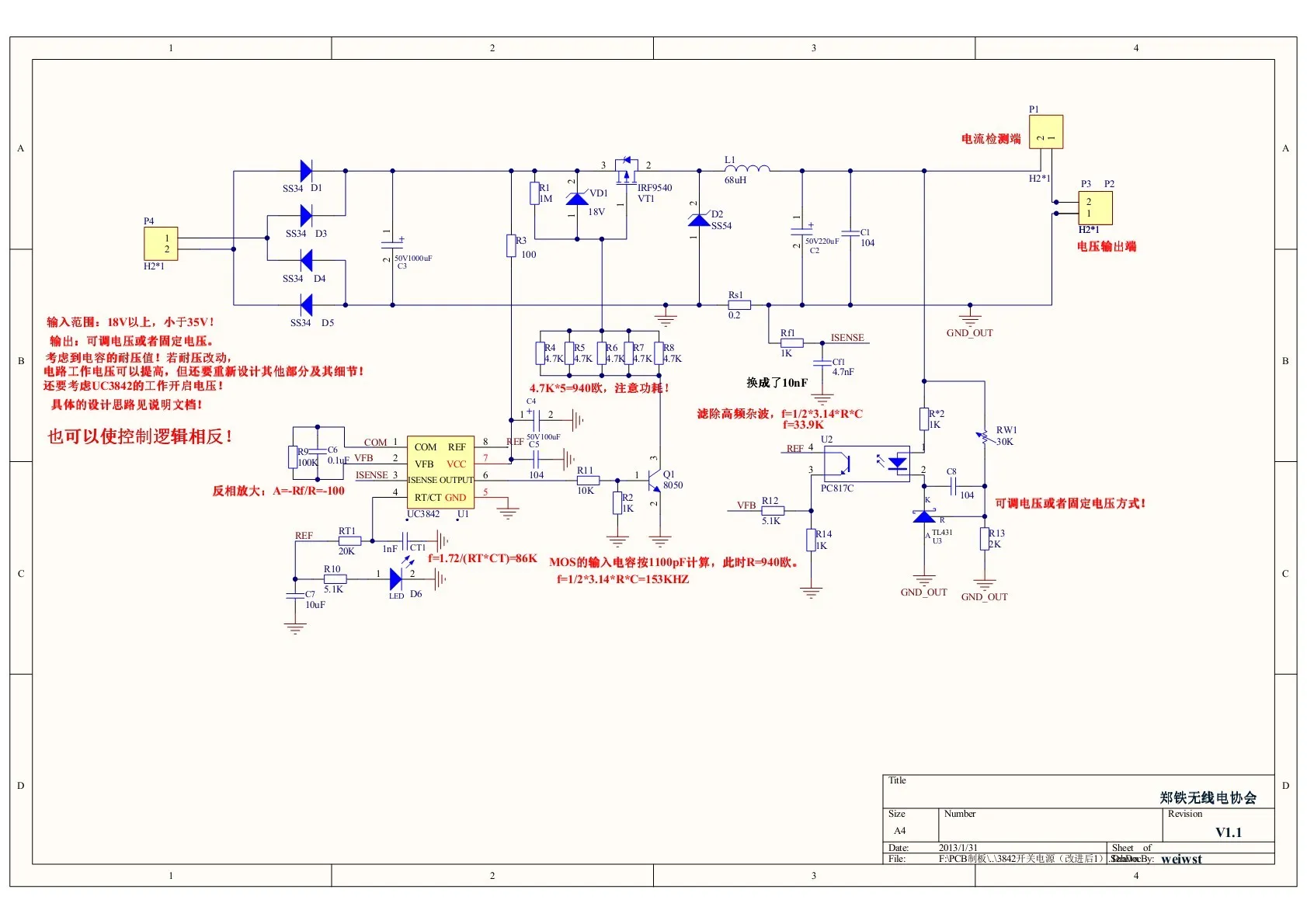

改進(jìn)后的就是V1.1的版本了。見(jiàn)原理圖:改進(jìn)了電流取樣電阻的位置,考慮到取樣電阻的電流變化將使電壓取樣端的變化變得不準(zhǔn)確且不穩(wěn)定,最好用隔離的形式使輸出的電壓變化反饋到芯片的電壓取樣端,就用了光耦隔離的形式。(這個(gè)電路只是畫(huà)了原理圖,沒(méi)有實(shí)際制作PCB。因?yàn)殡娐方Y(jié)構(gòu)變得復(fù)雜多了。這個(gè)電路圖從原理上應(yīng)該沒(méi)有大問(wèn)題了,但是如果看了后面的版本的試驗(yàn)就知道了,用三極管和穩(wěn)壓二極管的驅(qū)動(dòng)形式,驅(qū)動(dòng)波形還是不夠好的!)

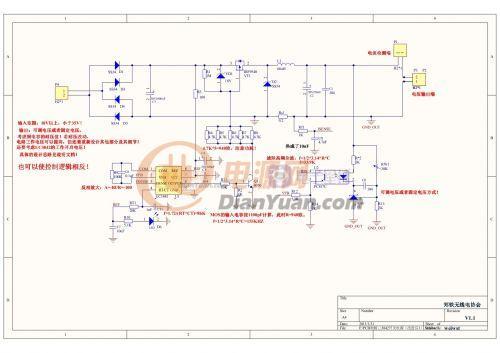

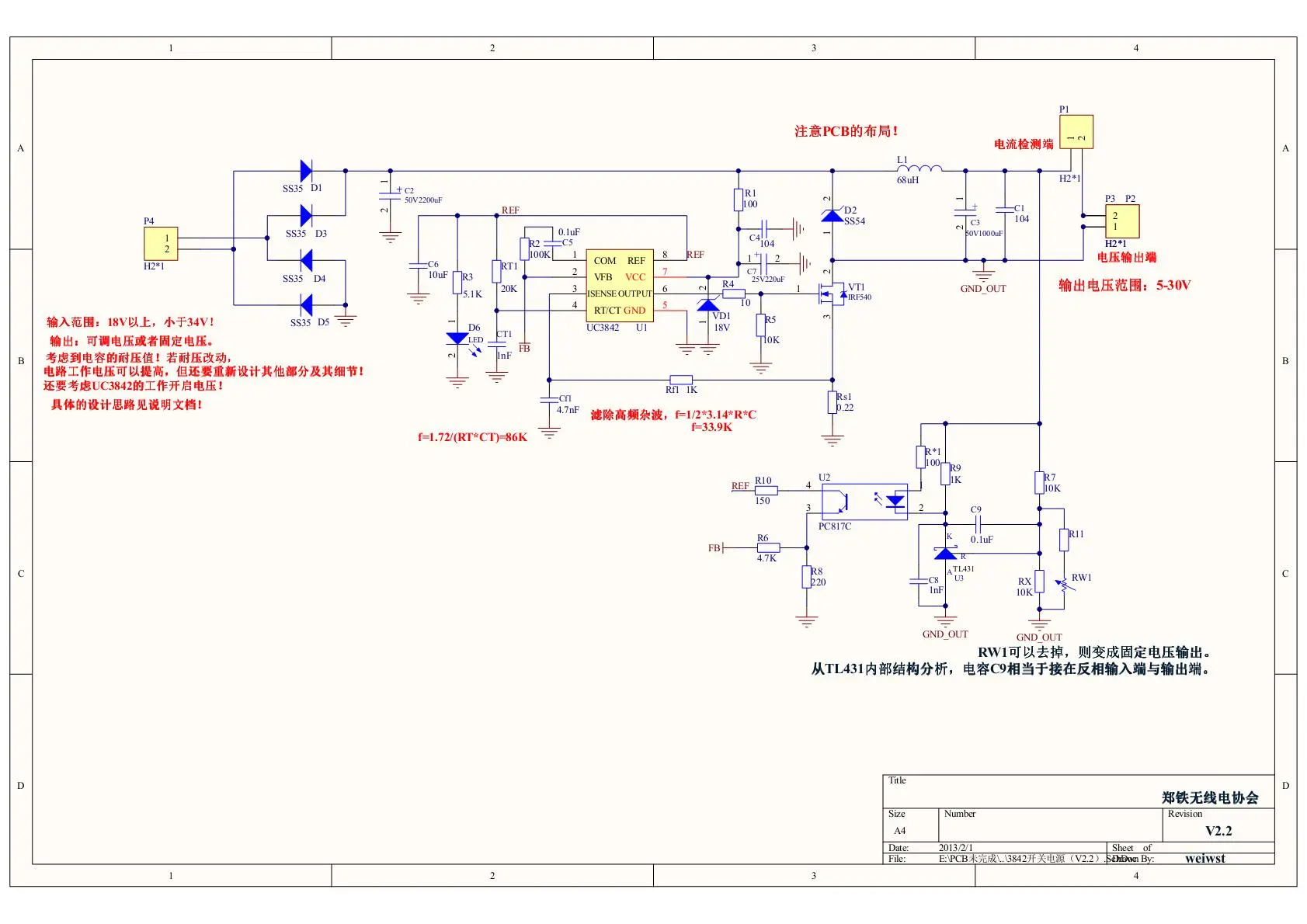

下面開(kāi)始分析第三版的電路V2.1版本,編號(hào)時(shí)煩了迷糊,沒(méi)有編號(hào)V2.0,直接就變成2.1了。根據(jù)群里的范工的指導(dǎo)、指點(diǎn),才有了下面的版本。MOS管變成了NMOS管,電路結(jié)構(gòu)變成了下面的形式。

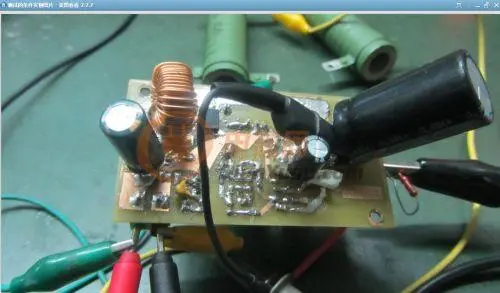

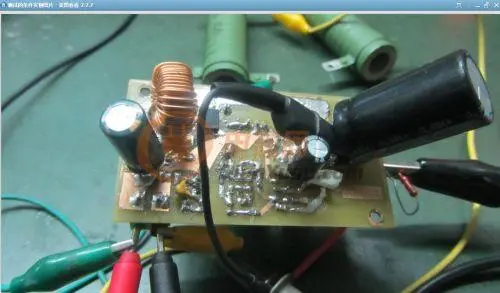

在V2.1版本的實(shí)際測(cè)試中,測(cè)試了很多組。改變了很多變量,圖片很多,在這里都張貼出來(lái)一定很煩人。就挑出比較有代表性的參數(shù)和圖片說(shuō)明問(wèn)題。

見(jiàn)上圖,測(cè)試時(shí)都是沒(méi)有很明確的思路,看到一個(gè)測(cè)試圖片,對(duì)圖中的參數(shù)的分析處理能力很差勁!當(dāng)然,能力都是要慢慢鍛煉出來(lái)的。

測(cè)試階段1:(當(dāng)時(shí)的測(cè)試條件也沒(méi)有記清晰,技術(shù)人員(雖說(shuō)我是業(yè)余的)應(yīng)該有一說(shuō)一,不知就是不知。不過(guò)后面的測(cè)試就好多了。)

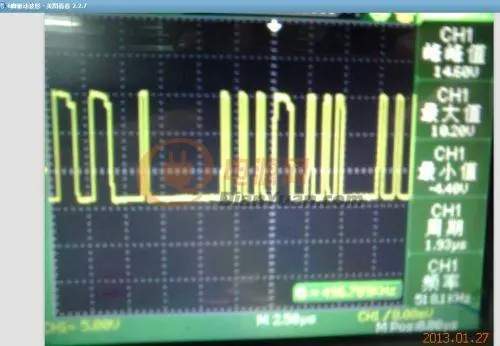

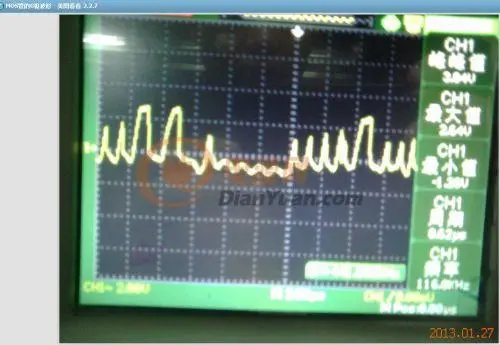

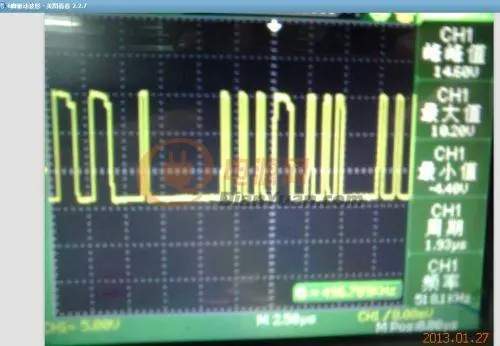

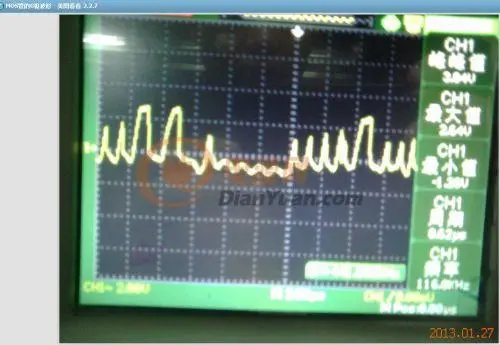

6腳芯片驅(qū)動(dòng)波形:

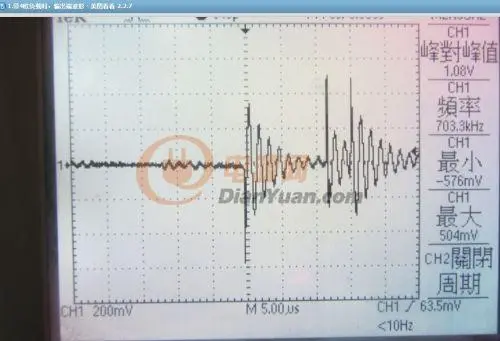

MOS管的G極波形:

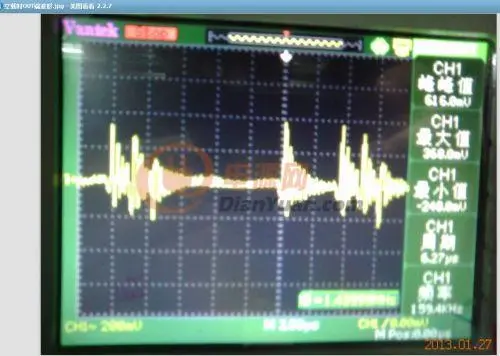

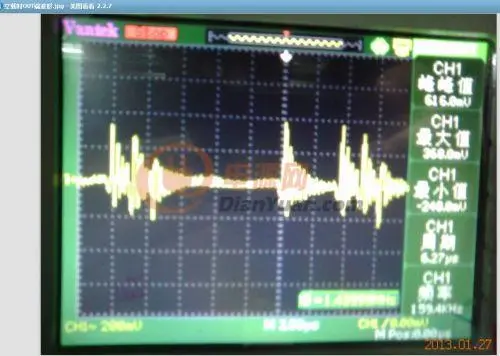

空載時(shí)OUT端波形:

從上面的測(cè)試結(jié)果可以看出,MOS管的驅(qū)動(dòng)波形在芯片輸出端還可以,但是到了MOS管的G極處卻變差了!當(dāng)然輸出端空載測(cè)量紋波等參數(shù)也是不恰當(dāng)?shù)模竺娴臏y(cè)試中已經(jīng)注意到了。

測(cè)試階段2:測(cè)試用的示波器是向老師借來(lái)的。

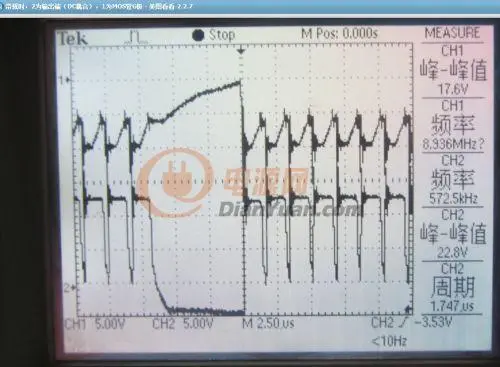

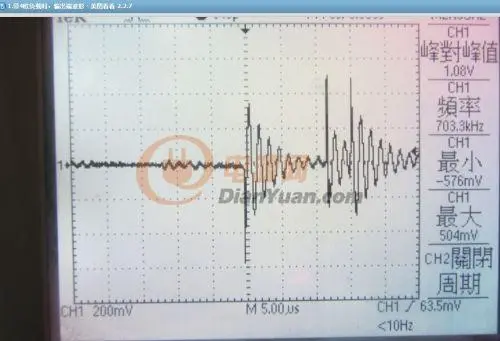

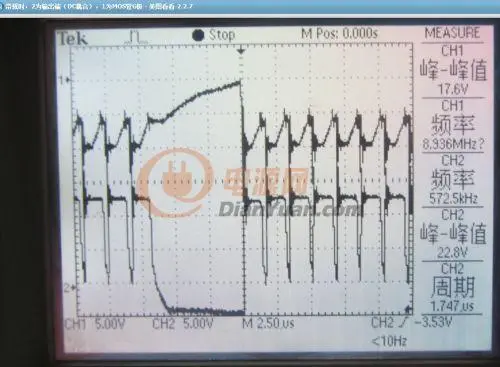

帶載時(shí),2為輸出端(DC耦合),1為MOS管G極:

空載時(shí),2為輸出端(AC耦合),1為MOS管G極:

從上面的兩個(gè)圖片中可以發(fā)現(xiàn)什么問(wèn)題呢?仔細(xì)看看,雖說(shuō)是用示波器同時(shí)測(cè)量的輸出端波形和MOS管的G極波形,但是也不應(yīng)該輸出是這種波形啊!再結(jié)合V2.1版本的原理圖來(lái)看。最后可以發(fā)現(xiàn):因?yàn)檫@兩個(gè)的地不是公共的地,它們之間的地是不同的,而示波器內(nèi)部的兩個(gè)通道是共地的!幸虧電壓不是太高,否則不知將出什么問(wèn)題呢。

既然測(cè)量方法是錯(cuò)誤的,那么這一組測(cè)量的就不能說(shuō)明問(wèn)題了!

說(shuō)到這里,不禁要延伸一下:關(guān)于紋波的測(cè)量,當(dāng)然不能用夾子線,最好也不能用探頭線(帶較長(zhǎng)的地線的)去測(cè)量紋波,以前也在制作用LM317,LM337等線性電源芯片制作電源的過(guò)程中遇到過(guò)測(cè)量方法的問(wèn)題,哪種才是正確的測(cè)量紋波的方法等問(wèn)題!還有PCB的布局問(wèn)題,旁路電容在電路中的正確布置方法等問(wèn)題!我很久以前的帖子有記錄,但是在這里卻注意的很少!真是不長(zhǎng)記性!詳細(xì)見(jiàn)21ic論壇“線性穩(wěn)壓電源,帶載能力,紋波很大!”具體的鏈接就不發(fā)了,因?yàn)樵?1IC曾經(jīng)發(fā)過(guò)被刪過(guò)一次帖子(最終雖說(shuō)又恢復(fù)了,但是記憶深刻),其中的利益關(guān)系就不觸犯了(很復(fù)雜,也許是我多想了)。這個(gè)帖子自己搜索吧,也算是鍛煉一下搜索能力!

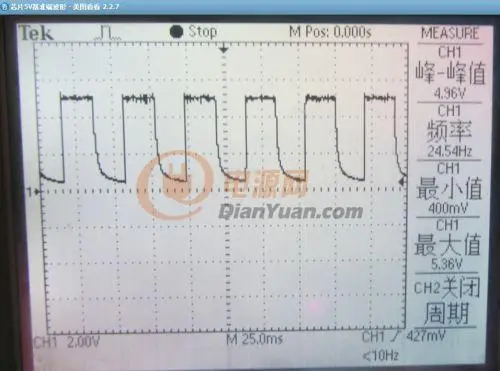

測(cè)試階段3,4:1K的電阻和4148去掉,換成10歐電阻,把18V穩(wěn)壓二極管連在芯片的VCC電源輸入端。(這樣原理圖的驅(qū)動(dòng)部分就變成了第四版的V2.2版本的電路了。為什么原來(lái)的驅(qū)動(dòng)不好,當(dāng)然是有測(cè)試的圖片了,原來(lái)是可以驅(qū)動(dòng),但是卻有些影響。)這些沒(méi)有在VCC端再并聯(lián)電容。此時(shí)的輸入電源不能使芯片的基準(zhǔn)很好工作。(從這些條件就可以知道原因。芯片間斷工作,因?yàn)榉€(wěn)壓管,也處于芯片的閉鎖范圍附近。)

3842的基準(zhǔn)端波形:

通過(guò)增加輸入端電壓和在芯片的VCC端多并電容的措施,上面的問(wèn)題解決了。

測(cè)試階段5,6,7,8:輸入電壓22V,使芯片供電電壓基本穩(wěn)定,前面并50V2200uF,后面并1000uF電容。

測(cè)試圖片:

使芯片供電電壓基本穩(wěn)定后,負(fù)載電流1A多.負(fù)載電阻4歐。取樣電阻由1.5K變成15K。輸出空載時(shí)為5.99V,4歐的負(fù)載,帶載后為5.83V。但是從電路參數(shù)的設(shè)置看,輸出電壓應(yīng)該是5V才對(duì)!

最后在群友的指導(dǎo)下,發(fā)現(xiàn)了問(wèn)題的所在。原因就是光耦反饋的部分的問(wèn)題,上面圖片中的R*1是1K的,最后變成了V2.2版本里的反饋部分變成了100歐。輸出電壓就變正確了。(反饋環(huán)路還是沒(méi)有設(shè)置好。)

就算是改動(dòng)后,輸出波形還是不太好。這里又花費(fèi)了很長(zhǎng)的功夫,最后還是群友在群友的幫助下,找到了問(wèn)題。

測(cè)試階段9,輸入22V,空載輸出4.99V,帶4歐負(fù)載輸出4.91V。(圖片和測(cè)試階段10的沒(méi)有本質(zhì)差別。)

測(cè)試階段10,輸入22V,空載4.99V,帶4歐為4.92V,帶2歐為4.88V。

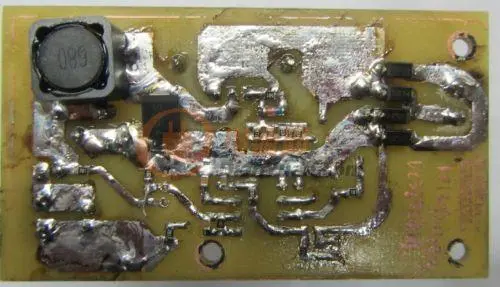

測(cè)試的實(shí)際圖片:(用的負(fù)載是功率電阻,每一個(gè)都是36W2歐。但是當(dāng)時(shí)沒(méi)有考慮到連接的導(dǎo)線的電阻,因?yàn)閷?dǎo)線太細(xì)了,電流大時(shí),其中的壓降也是不小的,根據(jù)功率電阻的阻值來(lái)計(jì)算的電流值就很不準(zhǔn)確了!)

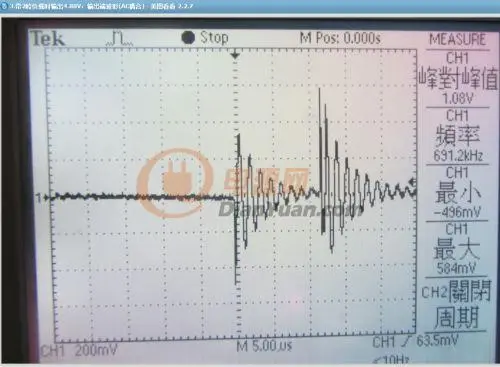

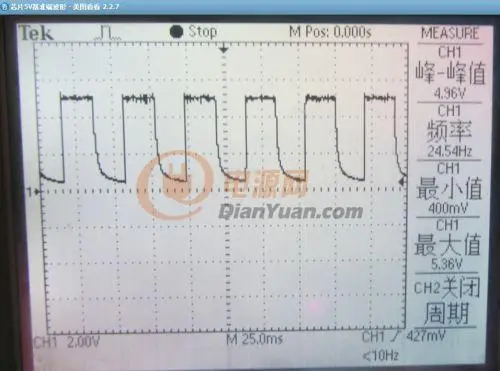

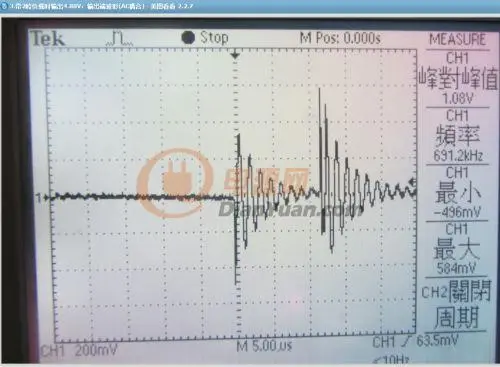

帶4歐負(fù)載時(shí),輸出端波形(AC耦合):

帶2歐負(fù)載時(shí)輸出4.88V,輸出端波形(AC耦合):

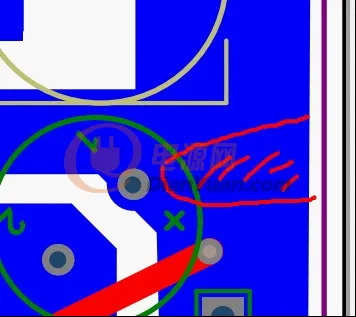

現(xiàn)在的性能還是不算太好。帶載后紋波上V了。有群友說(shuō),輸出的那個(gè)紋波是開(kāi)關(guān)噪聲,輸出上的噪聲和開(kāi)關(guān)管的動(dòng)作是同步的。輸入端關(guān)系不大,關(guān)鍵是輸出端。最后在群里中山-小廖的指導(dǎo)下,他發(fā)現(xiàn)我的PCB布局也有問(wèn)題!

輸出濾波電容沒(méi)有起到作用。

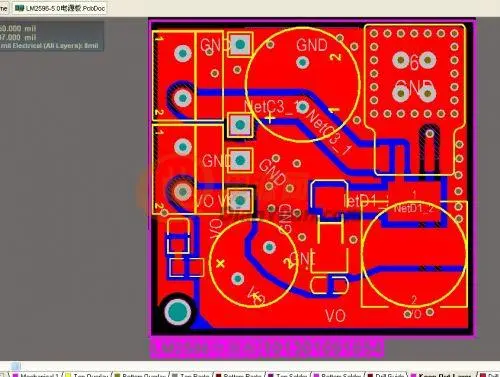

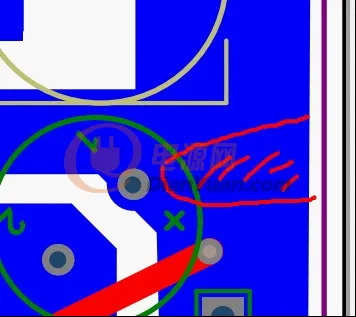

我的V2.1的原理圖和PCB布局。UC3842開(kāi)關(guān)電源V2.1:

把下圖中的輸出端的電路的紅色的那塊挖掉,否則電流是不會(huì)通過(guò)電容的如果是你走路的話,你會(huì)繞一下經(jīng)過(guò)電容還是直著走?

就這樣按照前輩的指導(dǎo),試驗(yàn)后效果明顯改善!繼續(xù)調(diào)試也沒(méi)有更多的改善,就這樣也許是整體布局的問(wèn)題。測(cè)試時(shí)也沒(méi)有保留圖片,就急著去改進(jìn)原理圖,也在V2.2版本的時(shí)候格外注意PCB的布局!協(xié)會(huì)在外面請(qǐng)的老師,他是在鄭州的電源工程師黃利平老師。

“2013年1月30日,今天下午黃老師來(lái)協(xié)會(huì)。給我和一個(gè)11級(jí)的同學(xué)解決最近的制作開(kāi)關(guān)電源的問(wèn)題。老師說(shuō)到了,電路的布局很重要,電容在電路中的位置,也講到了四角的電容。以及電源的環(huán)路盡量要小。

我們現(xiàn)在所采用的電源的結(jié)構(gòu),以及可以采用什么其他的電路結(jié)構(gòu)。將要遇到什么問(wèn)題,關(guān)鍵點(diǎn)在哪里等問(wèn)題。也從學(xué)弟的電路不能很好的工作,分析電路的問(wèn)題。MOS管的驅(qū)動(dòng)部分,哪些元件設(shè)計(jì)沒(méi)有必要,哪些不太合理等。從他采用的TL494的驅(qū)動(dòng)電路說(shuō)到了全橋驅(qū)動(dòng),脈沖變壓器驅(qū)動(dòng)以及磁芯的選取等。

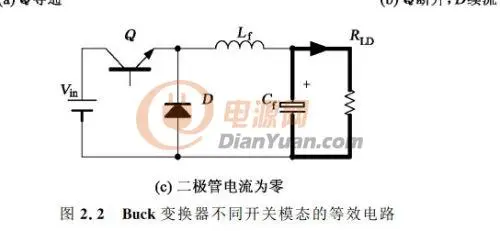

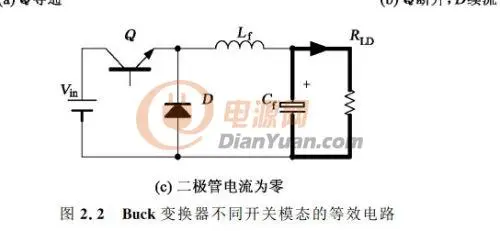

還說(shuō)了平時(shí)常用的另一種電路BUCK結(jié)構(gòu)的:

用脈沖變壓器驅(qū)動(dòng)NMOS管,或者用其他的驅(qū)動(dòng)MOS管的形式。

總之,先重新布局,看看性能如何,然后再試驗(yàn)這種形式。”